在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但不幸的是,这种信号并不存在。如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是抖动(jitter)。

2018-03-13 10:21

在time-based power analysis模式下,需要提供VCD或FSDB文件,工具会分析峰值功耗,并生成功耗波形等,SAIF格式对此不支持。

2022-10-24 16:49

时钟电路是芯片中最基础的电路,时钟电路性能的好坏关乎SoC中所有电路能否达到预期目标,例如:计算核(CPU/GPU/NPU)的主频,DDR的带宽,高速接口(PCIE)的带宽等。

2022-10-12 15:08

本系列,我们的产品技术专家将结合电子系统设计软件的新功能和应用热点进行选题,本期主题为Xpedition Schematic Analysis 原理图完整性分析工具简介,敬请参阅!

2024-09-24 10:00

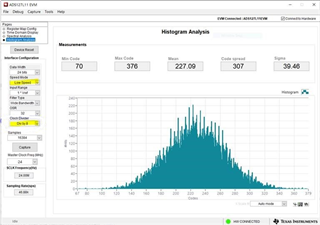

ADS127L11是德州仪器在2021年发布的高分辨率高采样率ΣΔADC,在评估其噪声和有效分辨率的时候可以运用本文论述的基于Histogram Analysis的方法。

2023-03-17 09:20

在开发过程中调整模型时,您需要检查所做的更改是否对模型性能有所改善。只检查准确度可能不够。

2019-04-29 17:42

PTPX,是基于PT,对全芯片进行power静态和动态功耗分析的工具。包括门级的平均功耗和峰值功耗。可以说PTPX就是PT工具的一个附加工具。

2022-10-24 16:55

SystemVue的Analyses中,总共包括4种分析方式,分别为Data Flow Analysis,Linear Analysis,Phased Array Analysis和RF system

2024-10-15 15:52

Discrete Jitter是由MMCM/PLL引入的,其具体数值可通过点击图2中Clock Uncertainty的数值查看,如图5所示。通常,VCO的频率越高,引入

2018-11-12 14:40