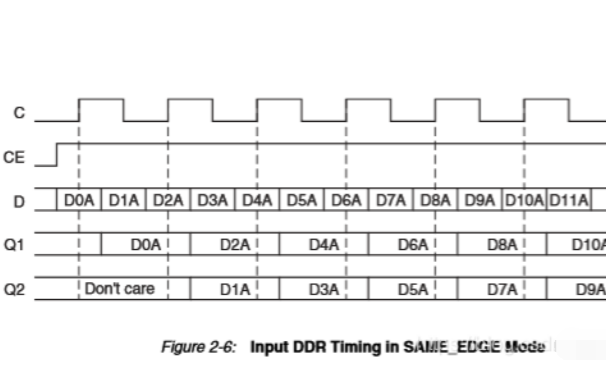

。 该结构类似于Virtex-6 FPGA实现。 图1 显示了使用OPPOSITE_EDGE模式的输入DDR的时序图。

2020-12-28 17:13

只能发生在FPGA的IOB上面,这里有特定的硬件结构可以实验上面单沿变双沿的方法,也就是使用原语进行一些列的操作。

2021-01-25 07:07

1.1 FPGA设计思想与技巧1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA双沿采样之IDDR原语实现;5)结束语。1.1.2 本节引言“不积跬步,无以至千里;不积

2021-07-26 06:37

亲爱的大家,Virtex中的许多原语在Spartan 6中找不到,例如BUFIO,BUFR,IDELAY,IDDR。如何使用Spartan原语实现类似的功能?非常感谢你!箱子以上来自于谷歌翻译以下

2019-06-03 10:31

SelectIO接口使用IDDR原语执行4x异步过采样。时钟由MMCM或PLL原语生成,并通过BUFG时钟网络路由,并可使用器件内任何选定的输入对单端或差分信号进行操作。XAPP523是由MMCM

2020-08-11 10:59

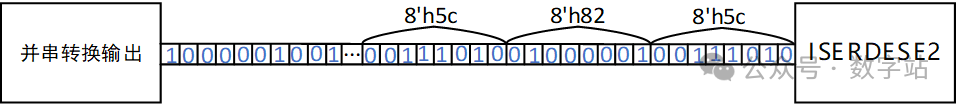

前面在讲解HDMI接口之前,讲解过IDDR、ODDR、OSERDESE2、IBUF等原语,之后一直有读者在问什么时候更新ISERDESE2这个原语。前文讲解过这些原语都

2025-03-17 10:52

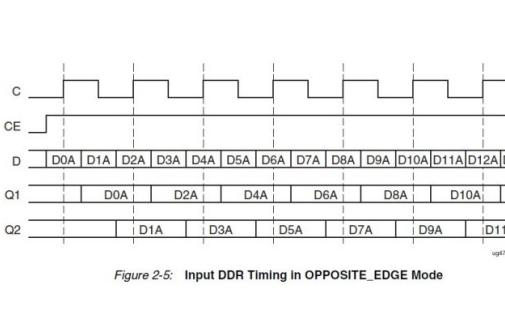

设计时延问题。图2 SAME_EDGE_PIPELINED模式中的输入DDR只需少量代码在《Virtex-4用户指南》的328~329页,举例说明采用VHDL和Verilog语言编写的IDDR原语的例化

2010-12-29 15:17

在7系列设备的ILOGIC block中有专属的registers来实现input double-data-rate(DDR) registers。这些特性可以通过实例化IDDR 原语实现。

2020-12-28 17:13

IDDR与ODDR的简述RGMII时序简述千兆网输入与输出模块的设计测试模块的设计仿真测试结果总结

2021-01-22 06:09

该设计元素是专用的输入寄存器,旨在将外部双数据速率(DDR)信号接收到Xilinx FPGA中。IDDR可用的模式可以在捕获数据的时间和时钟沿或在相同的时钟沿向FPGA架构显示数据。此功能使您可以避免其他时序复杂性和资源使用情况。

2021-03-13 09:07