由于各种逻辑电平的输入、输出电平标准不一致,所需的输入电流、输出驱动电流也不同,为了使不同逻辑电平能够安全、可靠地连接,逻辑电平匹配将是电路设计中必须考虑的问题。

2022-11-10 10:01

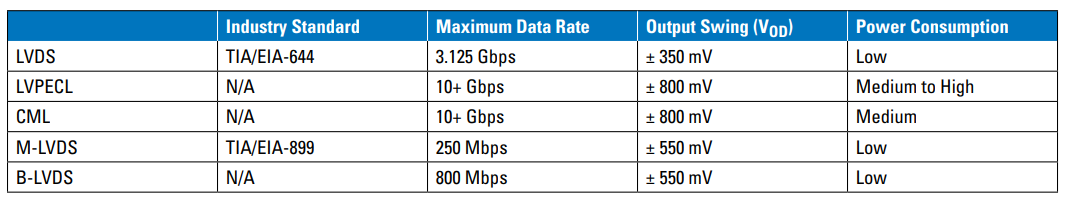

CML(Current-mode llogic)它并没有一个标准,是基于简单的差分放大器,如图2所示。通常取R1=R2=50欧姆,|VOUT+ - VOUT-| = R1 * i1 = 50*i1

2017-11-10 14:49

RS90LV049是一款双通道LVDS差分信号发送、接收一体的芯片,可以支持400Mbps的LVDS信号。

2025-02-10 17:19

LVDS(low-voltage differential signaling)即所谓的低压差分信号,它是一种小振幅差分信号技术,使用非常低的幅度信号(250~450mV)通过一对平行的PCB走线

2023-11-29 16:32

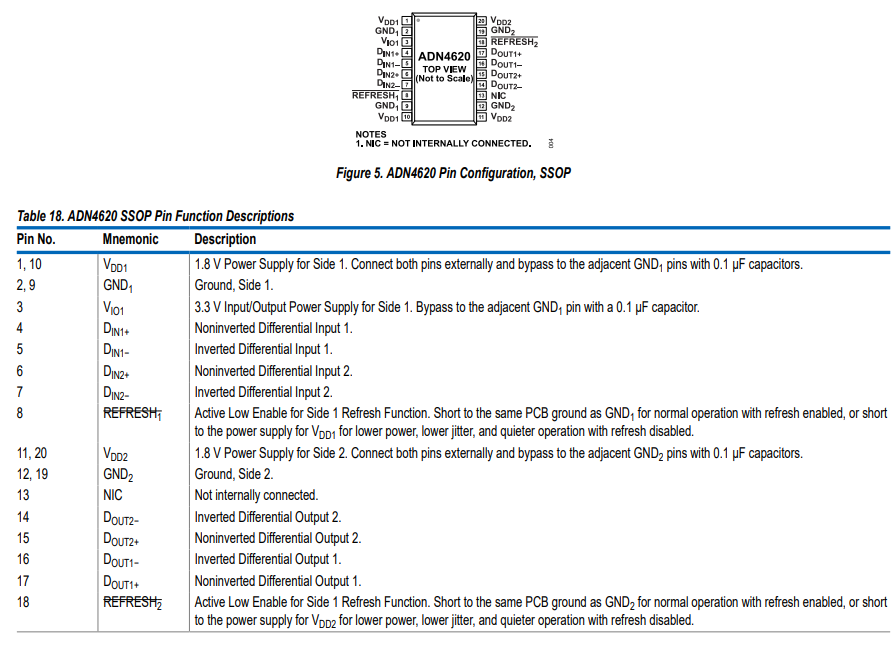

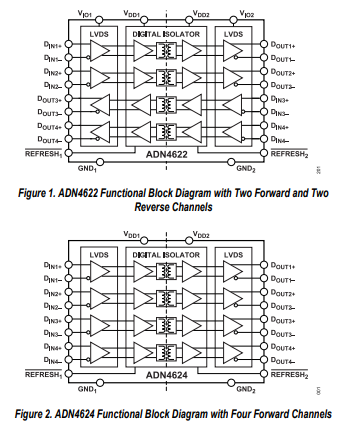

高速运行进行了增强,可提供LVDS信号链的插入式电气隔离。与LVDS接收器和LVDS驱动器之间的交流耦合和/或电平转换允许隔离其他高速信号,例如电流模式逻辑(CML)。

2025-05-29 14:42

什么是LVDS,LVDS的全称是Low-Voltage Differential Signaling ,即低电压差分信号。LVDS可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。

2020-11-01 10:03

*Coupler^®^ 技术,已针对高速运行进行增强,可提供 LVDS 信号链的插入式电气隔离。到 LVDS 接收器和来自 LVDS 驱动器的交流耦合和/或电平转换允许隔离其他高速信号,例如电流模式逻辑 (

2025-05-29 14:37

LVDS 采用了差分传输机制,每一 LVDS 信号使用两条走线。 这两条走线之间的电压差定义了 LVDS 信号值。

2020-03-22 15:54

这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bit LVDS接口。此,也称18位或18bit LVDS接口。

2023-06-02 16:01

LVPECL即Low Voltage Positive Emitter-Couple Logic,也就是低压正发射极耦合逻辑,使用3.3V或2.5V电源,LVPECL是由PECL演变而来的。

2017-04-26 10:16