接上文提到有没有更简便的方法可以不做那么复杂的弯针模型呢?模型建立越接近真实情况固然越准确,但是耗费时间,准确和效率找到平衡才是智者所为。

2023-12-12 15:44

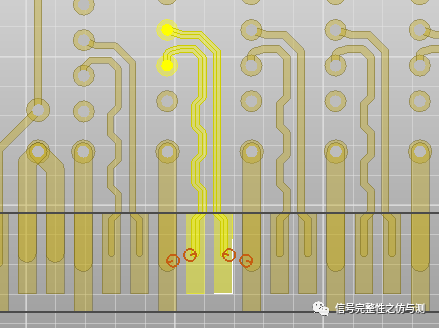

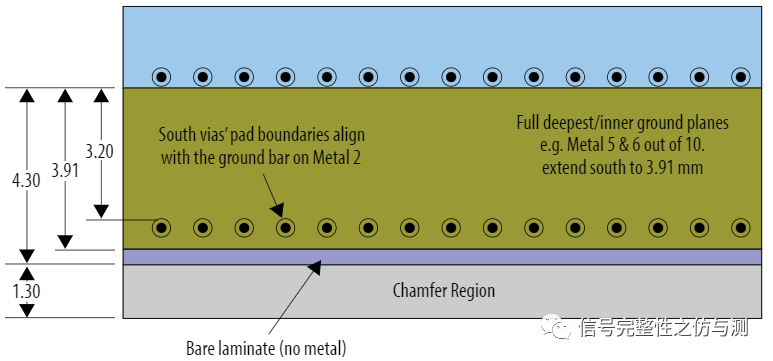

金手指是沿着印刷电路板 (PCB) 的连接边缘看到的镀金柱。金手指的目的是将辅助PCB连接到计算机的主板上。PCB金手指还用于通过数字信号进行通信的各种其他设备,例如消费者智能手机和智能手表。金用于PCB的连接点,因为合金具有优异的导电性。

2023-12-12 15:42

随着汽车行业的快速发展,汽车电子电气架构正在从传统的分布式向多域融合的集中式转变。同时,高级驾驶辅助系统(ADAS)的大规模部署,正有力推动着汽车行业向更高等级的自动驾驶迈进。这些革新技术反过来又加速了汽车从以硬件为中心的模式,向软件定义汽车(SDV)模式的转变。而所有这些变革都在推动着业内对SoC需求的增加,以支持更高的计算需求。除了SoC之外,构建一个可靠且开放的开发环境也是塑造未来汽车并助力其持续演进的必要条件。

2024-12-29 17:12

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen

2023-06-08 15:29

Compute Express Link 是一种缓存一致性互联,旨在帮助系统(尤其是具有加速器的系统)更高效地运行。CXL位于 PCIe Gen5链路基础架构之上。可以有 PCIe Gen5 设备

2022-03-23 15:26

在该FPGA器件的外围,这个硬2D NoC连接到所有高速接口:包括多个400G以太网、PCIe Gen5、GDDR6和DDR4/5端口。这使得Achronix的Speedster7t成为了业界第一款

2023-11-24 16:19

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

2024-11-05 15:45

这款移动GPU的测试平台为桌面Z390主板+i7-9700,显卡为测试版的Gen 12 移动显卡,也就是Xe架构的GPU。这款Gen 12 移动显卡为96组CU,GPU频率最高为1.5GHz,显存为3GB。

2020-03-05 17:32

新洁能650V Gen.7系列IGBT产品,基于微沟槽场截止技术,可大幅提高器件的元胞结构密度。采用载流子存储设计、多梯度缓冲层设计、超薄漂移区设计,大幅度提升器件的电流密度。同时优化了器件的开关特性,为系统设计提供更大的余量。

2024-08-15 16:34

Rapid IO协议由于无主机,且各设备之间可以并行交换信息,所以广泛应用于对交换速率要求高,且交互复杂的应用中。Xilinx现在有支持Serial RapidIO Gen2的核,可以应用在此场景中

2018-06-29 09:02