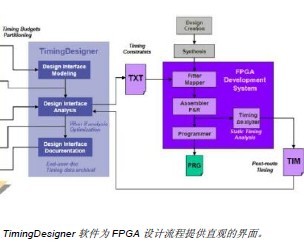

一、摘要 从简单SRAM接口到高速同步接口,TimingDesigner软件允许设计者在设计流程的初期就判断出潜在的时序问题,尽最大可能在第一时间解决时序问题。在设计过程的早期检测到时序问题,不仅节省时间,而且可以更

2011-01-13 16:25

1、FPGA中的时序约束--从原理到实例 基本概念 建立时间和保持时间是FPGA时序约束

2022-11-15 15:19

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的

2015-09-05 21:13

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45

的文件qxp中,配和qsf文件中的粗略配置信息一起完成增量编译。 4. 核心频率约束+时序例外约束+I/O约束+LogicLock LogicLock是在FPGA器件底

2016-06-02 15:54

时序分析是FPGA设计的必备技能之一,特别是对于高速逻辑设计更需要时序分析,经过基础的FPGA是基于时序的逻辑器件,每一

2017-02-26 09:42

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA

2021-07-26 06:56

c6678中的上电复位时序控制的FPGA程序。有两个版本,一个是TI公司的,一个是我们自己公司的。

2016-03-07 12:34

本帖最后由 小墨学FPGA 于 2015-4-15 16:38 编辑 七、SDRAM工作时钟相位偏移计算从上篇文章中我们知道,我们的数据是要经过一定的延时才会到达目标器件的,这个延时也就

2015-03-31 10:35

时钟。 例如,输入的时候,源寄存器在SDRAM中,目的寄存器在FPGA中,数据的传输是在SDRAM工作时钟下进行的,但是时序分析工具不知道这个时钟,所以我们定义一个虚拟

2015-03-31 10:20