的应用。在主流的FPGA中,绝大多数都采用了SRAM来存放配置数据,称为SRAM FPGA。这种FPGA的突出优点是可以进行多次

2018-07-18 12:50

ISE12.2设计套件强化了其部分可重配置技术设计流程,并通过智能时钟门控技术降低24% 的 BRAM 功耗。赛灵思部分可重配置技术,是目前唯一经行业验证的

2010-07-31 12:39

基于SRAM的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存字的配置数据决

2009-06-20 11:05

通过FPGA的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI F

2014-01-24 14:17

关键词:PLD , SRAM , 可重配置电路 由于SRAM的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使

2019-02-23 14:30

Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。

2021-07-05 15:28

采用VC++程序的FPGA重配置设计方案利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储于存储器的不同系统数据

2010-04-14 15:14

应用而设计的基于FPGA的赛灵思可重配置加速堆栈,包括库、框架集成、开发板并支持OpenStack。通过赛灵思FPGA,该可

2018-07-31 09:08

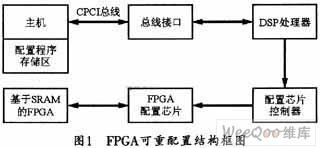

结合对FPGA重配置方案的软硬件设计,本文通过PC机并通过总线(如PCI总线)将配置数据流下载到硬件功能模块的有关配置芯片,从而完成

2018-12-30 09:26

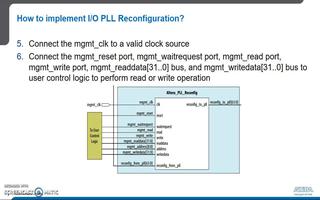

如何在 Arria 10 中实现 I/O 锁相环 (PLL) 重配置

2018-06-20 00:57