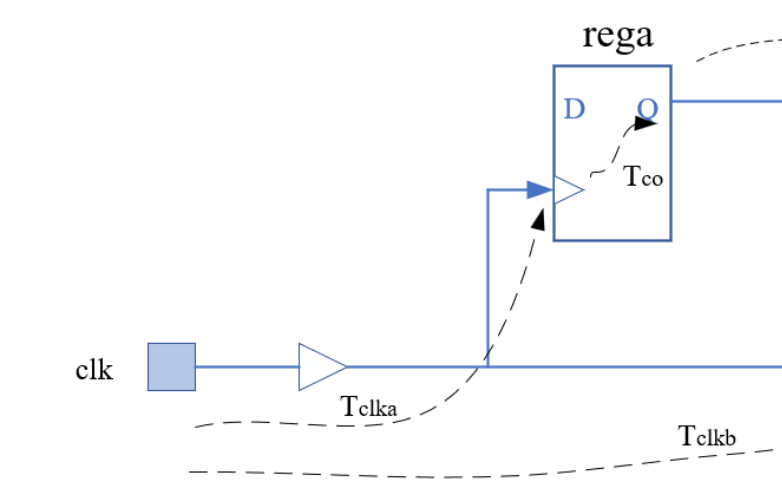

组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对时钟延迟和Tdata做一定的要求或

2021-01-12 17:31

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序

2015-09-05 21:13

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45

目录Arduino实践详细说明(三)L298N驱动直流电机L298N说明接口说明正反转及调速说明接线

2021-06-29 08:06

好的时序是设计出来的,不是约束出来的时序就是一种关系,这种关系的基本概念有哪些?这种关系需要约束吗?各自的详细情况有哪些

2018-08-01 16:45

本文档的主要内容详细介绍的是电子管的代换资料详细说明。

2023-09-26 07:24

FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在

2016-06-02 15:54

hex文件格式详细说明

2013-11-13 12:37

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在

2021-07-26 06:56

50Mhz来驱动网口正常工作,也可以用MCO1。这里的详细倍频分频选择网口模块的配置再详细说明。不需要MCO输出频

2021-08-03 06:23