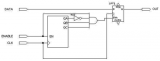

当你需要将FPGA/CPLD内部的信号通过管脚输出给外部相关器件的时候,如果不影响功能最好是将这些信号通过用时钟锁存后输出。因为通常情况下一个板子是工作于一种或两种时钟模式下,与FPGA/

2017-02-11 13:18

在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统

2017-02-11 13:04

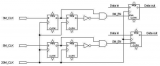

注意:当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己。 需要说明的是在FPGA/CPLD内部结构是一种标准的宏单元,下图是Xilinx公司的Spartans

2017-02-11 13:14

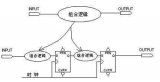

异步设计不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。

2017-02-11 13:11

当产生门控时钟的组合逻辑超过一级(即超过单个的“与”门或“或”门)时,证设计项目的可靠性变得很困难。

2017-02-11 13:28

数字电路设计 关于高速数字电路的电气特性,设计重点大略可分为三项: 正时(Timing) :由于数字电路大

2009-08-26 19:08

数字电路设计是数字电路最为关键及重要的一步,今天我们将从各个流程为大家介绍完整的数字电路设计!

2022-07-10 17:14

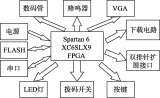

数字电路作为一门专业基础课,除了介绍数字电路的理论知识外,更需要通过配套的实验平台将理论知识和实践环节相结合,培养学生的动手能力和实践创新能力。

2020-08-16 12:03

高速数字电路设计 关于高速数字电路的电气特性,设计重点大略可分为三项 : Ø 正时 (Timing) :由于数字电路大多依据时脉信号来做信号间的同

2007-10-16 17:22

可编程逻辑器件PLD(Programmable Logic De-vice)是一种数字电路,它可以由用户来进行编程和进行配置,利用它可以解决不同的逻辑设计问题。

2020-04-28 11:18