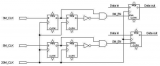

当你需要将FPGA/CPLD内部的信号通过管脚输出给外部相关器件的时候,如果不影响功能最好是将这些信号通过用时钟锁存后输出。因为通常情况下一个板子是工作于一种或两种时钟模式下,与FPGA/

2017-02-11 13:18

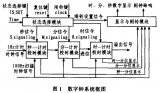

在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统

2017-02-11 13:04

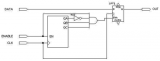

注意:当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己。 需要说明的是在FPGA/CPLD内部结构是一种标准的宏单元,下图是Xilinx公司的Spartans

2017-02-11 13:14

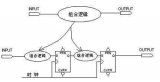

当产生门控时钟的组合逻辑超过一级(即超过单个的“与”门或“或”门)时,证设计项目的可靠性变得很困难。

2017-02-11 13:28

异步设计不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。

2017-02-11 13:11

使用Verilog进行数字电路设计是一个复杂但有序的过程,它涉及从概念设计到实现、验证和优化的多个阶段。以下是一个基本的步骤指南,帮助你理解如何使用Verilog来设计数字电路: 1. 明确设计需求

2024-12-17 09:47

在当今电子技术行业发展过程中,对高速电路数字设计十分关注,高速数字电路是利用多个电子元件组成的,可以让计算机高速数字电路技术进一步提高,因此在计算机中使用高速数字电路设计

2020-08-21 17:41

本文介绍了EDA技术主要特点和功能,并对将EDA技术引入到数字电路设计工作方案进行了探讨。##EDA技术在数字系统中应用以基于AlteraEPM7128SLC84-15芯片和MAX PlusII 10.0软件平台数字

2014-01-24 14:38

对于高速数字电路而言,虽然还是关注电压,但是其设计方法和射频电路的设计方法相近,也需要考虑阻抗阻抗匹配,因为反射电压的存在会导致额外的误码率

2016-05-26 15:42

采用FPGA进行的数字电路设计具有更大的灵活性和通用性,已成为目前数字电路设计的主流方法之一。

2019-07-24 09:06