本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD

2010-11-04 10:11

都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果

2023-05-18 08:56

Xilinx和数据接口相关的常用约束有Period、OFFSET_IN_BEFORE、OFFSET_IN_AFTER、OFFSET_OUT_BEFORE 和 OFFSET_OUT_AFTER;

2023-05-13 10:27

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD

2017-12-02 11:30

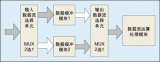

常用FPGA/CPLD四种设计技巧 FPGA/CPLD的设计思想与技巧是一个非常大的话题,本文仅介绍一些常用的设计

2010-05-12 11:10

可编程逻辑包括 PAL、GAL、PLD 等。通过不断发展,它已经发展成为现在的CPLD/FPGA。CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)的功能基本

2023-07-03 14:33

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域

2017-10-24 10:04

FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即L

2018-04-17 17:02

本文主要介绍CPLD和FPGA的基本结构。 CPLD是复杂可编程逻辑器件(Complex Programable Logic Device)的简称,FPGA是现场可编程

2020-09-25 14:56

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。C

2024-01-23 09:17