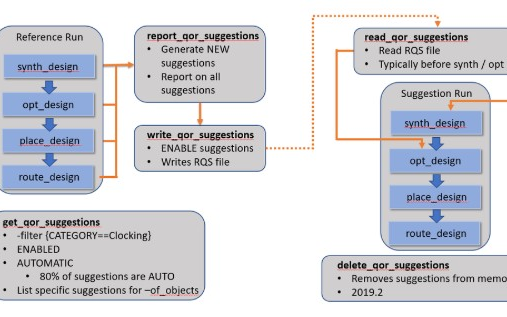

Report QoR Suggestions (RQS) 可识别设计问题,并提供工具开关和可影响工具行为的设计单元属性的解决方案,即便在无法自动执行解决方案的情况下也可提供文本修改建议。

2020-01-24 17:27

report_failpast除了基本的使用方法(不添加任何选项)之外,还提供了其他的选项。例如,-pblock选项可用于分析Pblock对应的约束是否合理。该选项可在布局之前使用(要求已经提供了Pblock具体位置约束),也可在布局之后使用。

2018-11-13 10:35

NVIDIA Blackwell白皮书:NVIDIA Blackwell Architecture Technical Brief

2025-03-20 18:35

这次我们要介绍的GUI上的按键是Summary Report。这个按键其实很简单,就是调用summaryReport这个命令,点一下会出现如下界面

2020-05-19 16:49

Report QoR Suggestions (RQS) 可识别设计问题,并提供工具开关和可影响工具行为的设计单元属性的解决方案,即便在无法自动执行解决方案的情况下也可提供文本修改建议。

2023-07-19 10:38

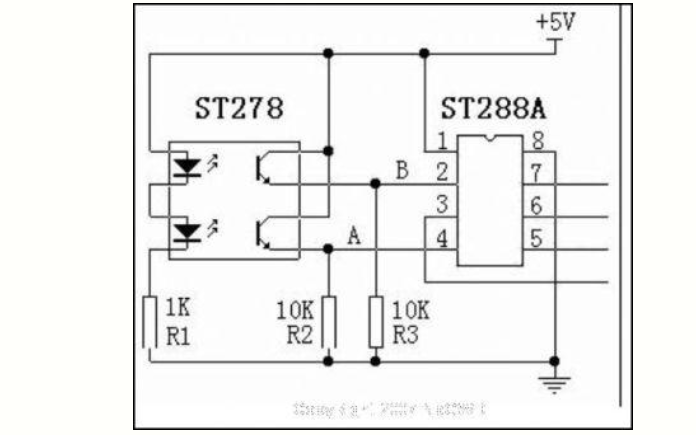

ST288A、ST289AX2、ST289AX4为方向判别专用集成电路,八脚双列直插封装或表面贴装,美国制造,工作电源5V,具有集成度高,功耗小静态电流约为1mA,抗干扰能力强等特点,外围只需加少许接口器件。

2019-10-13 09:19

本应用笔记介绍了适用于ISM频段(包括315MHz、433.92MHz、868.35MHz和915MHz)的幅度移控(ASK)发射器的FCC和ETSI辐射限值。讨论证明符合这些限制所需的特定测试

2023-03-08 15:15

本文中,我们利用连续电感器电流条件下有源钳位正向转换器的峰值电流模式(PCM)改进型小信号模型,预测UCC289X应用的实际环路稳定性。为了验证计算结果的有效性,我们通过实际测量基于UCC2897

2013-10-15 09:39

如果选择Synth and Impl,会生成两个文件:RQSPreSynth.tcl和RQSImplCommon.tcl。Project模式下,RQSPreSynth.tcl可作为约束文件直接添加到Constraint Set里(Vivado支持.tcl文件作为约束文件,添加时将文件类型切换为.tcl即可,如图6所示)。

2019-01-15 16:48

《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20