时序分析基本概念介绍——Timing Arc

2018-01-02 09:29

然后会出现如下窗口, 使用GTD前, 需要有一个machine readable格式的timing report文件, 该文件可以通过report_timing -machine_readable

2020-05-19 16:14

Digital Twin意为数字双胞胎,或数字孪生、数字映射等等,业界翻译众多。

2019-06-06 13:46

DIGITAL LINK是Panasonic的一种基于HDBaseT技术的连接系统,支持HDMI信号、未压缩4K(4.2.0)视频、全高清视频、音频和控制命令的传输,通过一根局域网电缆,在长距离模式

2024-09-19 10:11

有时候在debug GT的时候,需要用Digital monitor读出RX equalizer的code,本篇文章以US+的GTM为例子,提供了一个步骤,详细寄存器可以参考UG581.

2023-12-16 10:27

此款高速数据传输适配器专用于Digital Discovery,用以替代普通的2×16 Flywire信号线组件。通过将其连接在Digital Discovery的DIN_USR接口上,用户可以在

2019-11-13 17:15

《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20

随着设计复杂度和调用 IP 丰富度的增加,在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,用户在 XDC 里面并没有指定 set_false_path,为什么有些路径在分析时忽略了?那怎么去定位这些约束是哪里设定的?

2022-09-15 10:24

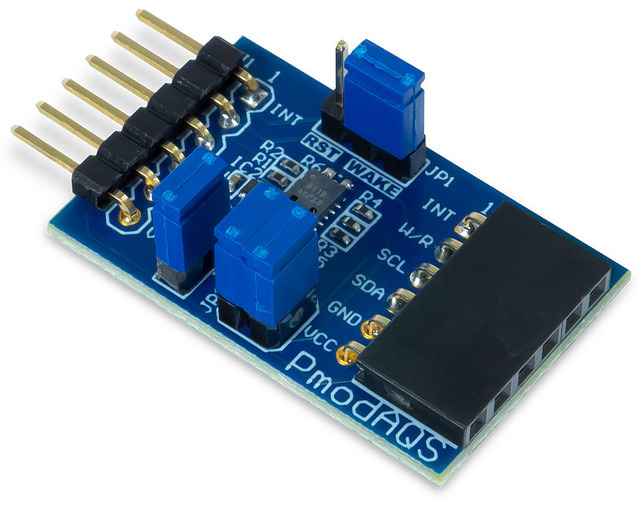

Digilent Pmod AQS是一种数字气体传感器,用于以低功率监测室内空气质量。 使用AMS CCS811,您可以使用微加热板技术检测各种挥发性有机化合物(VOC),为气体传感器提供高度可靠的解决方案,并缩短循环时间。

2019-11-27 14:19

Ω Digital Smart K数字音频功放产品AW88166FCR。此新产品AW88166FCR非常适用于多声道终端设备(如平板等)和各类IoT设备(手表、AR、VR等)对好音质和大响度的应用需求。

2023-05-14 10:32