当SoC上有超过80%的芯片面积被各种形式的存储器占用之时,存储器的DFT测试已经变得非常重要。

2023-12-09 09:56

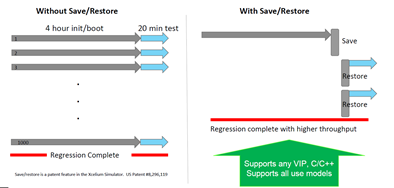

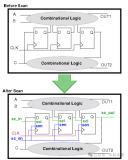

当今片上系统的设计复杂性日益增加,可能导致长达数小时、数天甚至数周的可测试性 (DFT) 仿真设计。由于这些往往发生在专用集成电路(ASIC)项目结束时,当工程变更单(ECO)强制重新运行这些长时间

2023-04-20 10:21

本文介绍了对高速宽带宽信号链的噪声性能进行理论分析所需的步骤。尽管选择了特定的信号链进行分析,但突出显示的步骤可以认为对任何类型的信号链都有效。

2022-12-14 16:29

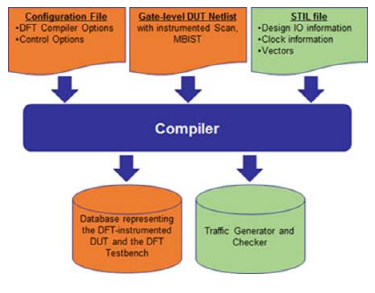

DFT 可以降低通过问题器件的风险,如果最终在实际应用中才发现器件有缺陷,所产生的成本将远远高于在制造阶段发现的成本。它还能避免剔除无缺陷器件,从而提高良率。插入 DFT 亦能缩短与测试开发相关的时间,并减少测试装配好的芯片所需的时间。

2019-09-16 14:31

Ad-hoc DFT 包括一套提倡“良好”设计规范的规则,旨在简化和加速测试流程。例如,提供置位和复位信号,使得所有触发器均可初始化;避免引起振荡的异步逻辑反馈;逻辑门设计应注意避免扇入数过大(扇入

2018-04-12 14:29

的计算能力和相当多的时间。分层可测试性设计通过在区块或内核上完成了 DFT 插入和图案生成解决了这个问题。

2018-01-31 07:06

时间频率测量是电子测量的重要领域。频率和时间的测量已越来越受到重视,长度、电压等参数也可以转化为与频率测量有关的技术来确定。本文通过对传统的多周期同步法进行探讨,提出了多周期同步法与量化时延法相结合的测频方法。

2020-07-21 15:01

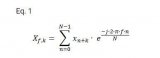

滑动DFT的推导是相当简单的,并且和DFT完全等价。也就是说,滑动DFT算法相比传统DFT或FFT算法没有信息丢失或失真。下面有完整的推导过程,没有兴趣的读者可以跳过这

2018-02-19 01:01

在芯片设计的世界里,有一种被称为"火眼金睛"的技术,它就是DFT(Design for Testability,可测性设计)。今天,就让我们一起揭开这项技术的神秘面纱,看看它是如何成为芯片质量的守护神的。

2025-03-01 09:49

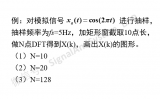

在DFT谱分析中,当DFT点数N大于数据本身的实际点数L时,相当于在数据后面补上了L-N个0再做DFT,称为“补零DFT

2019-05-07 14:09