1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器

2020-12-31 11:17

为了满足高速图像数据采集系统中对高带宽和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的设计方法,提出了一种基于Verilog-HDL 语言的DD

2017-11-17 14:14

学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相

2019-11-10 10:28

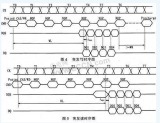

。使用开发软件Quartus II 中内嵌的逻辑分析仪SignalTap II 对控制器的工作流程进行了验证和调试。最终采集到的数据波形表明,完成了对DDR SDRAM 的突发读写操作,达到了预期设计的目标。

2019-08-14 08:00

摘 要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器的设计方法,使用该方法实现的控制器可非

2009-06-20 13:04

提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情

2017-11-22 07:20

设计和功能对于提升系统性能、降低功耗以及增强数据可靠性起着至关重要的作用。以下是对DDR4 SDRAM控制器主要特点的详细分析,旨在覆盖其关键

2024-09-04 12:55

基于FPGA的高速SDRAM控制器的视频应用 0 引言 SDRAM(同步动态存储器

2009-11-04 09:56

数据的基本方式,但DDR2却拥有2倍的DDR预读取能力(即4位预存取技术)。此外,DDR2还增加ODT(内建核心终结电阻器

2017-11-25 01:41

DDR SDRAM的接口特性:其输入输出引脚与SSTL-Ⅱ电气特性兼容,内部提供了DDR触发器、锁相环等硬件资源。使用这些特性,可以比较容易地设计性能可靠的高速

2017-11-24 16:00