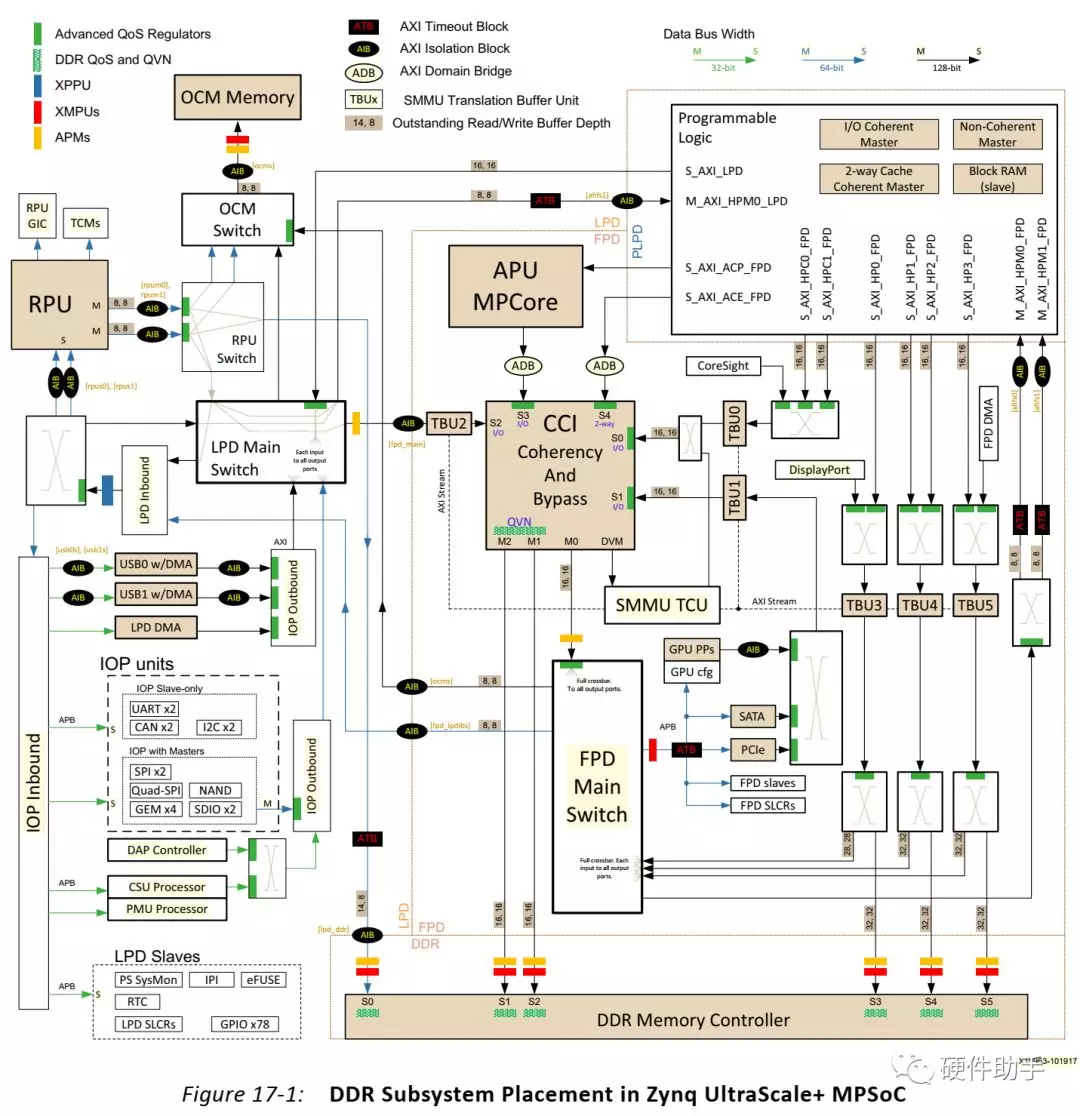

本篇主要针对Zynq UltraScale + MPSoC的DDR接口,从硬件设计的角度进行详细介绍,最后展示一下小编之前自己设计的基于ZU+的外挂8颗DDR4的设计。 目前比较常用的

2021-09-16 10:17

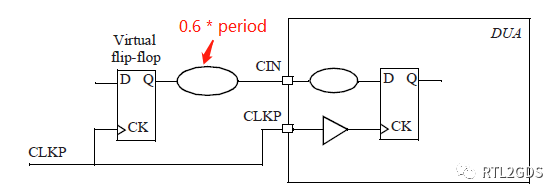

IO约束在顶层和模块级的主要命令都是以下几个,但是实际应用的复杂程度不可同日而语,本篇会先介绍模块级IO约束实战经验,然后讲解顶层IO约束复杂性,过程中会介绍DDR接口时序。

2023-06-27 15:07

随着航天技术的发展,FPGA 等大规模逻辑器件越来越成为不可缺的角色。

2018-08-02 17:41

DDR接口速率越来越高,每一代产品都在挑战工艺的极限,对DDR PHY的训练要求也越来越严格。本文从新锐IP企业芯耀辉的角度,谈谈DDR PHY训练所面临的挑战,介绍芯

2024-01-05 10:27

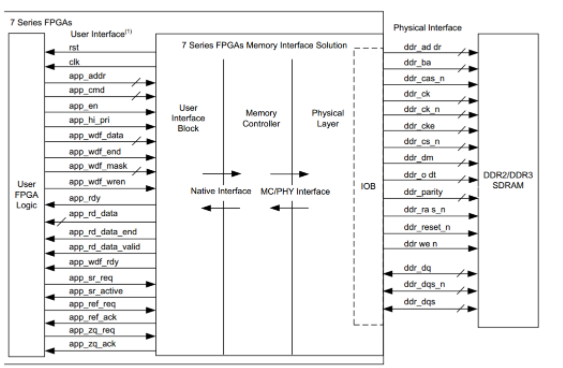

Memory Options这页输入时钟周期选择为200MHz,根据Controller Options页的选项,该时钟经过PLL分频和倍频后的时钟分别作为用户侧时钟100MHz和DDR接口时钟400MHz。

2020-10-29 14:44

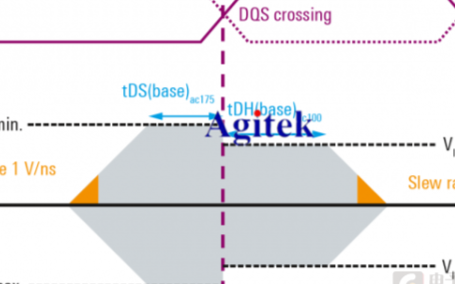

现代计算机系统的许多接口都采用了DDR技术,其中之一涉及到处理器与内存的工作方式,人工智能(AI)、机器学习(ML)和数据挖掘等新应用也在不断推动这种接口突破新的极限。针对高带宽同步

2023-02-22 10:46 深圳(耀创)电子科技有限公司 企业号

工程师要快速检查信号质量,眼图测试有助于在极短时间内获悉信号完整性状况。 测试 DDR 接口信号质量时,数据眼图分析有助于揭示潜在的信号完整性问题。因此,许多信号完整性工程师都使用眼图功能迅速测定

2020-07-23 15:50

本篇主要针对Zynq UltraScale + MPSoC的DDR接口,从硬件设计的角度进行详细介绍,最后展示一下小编之前自己设计的基于ZU+的外挂8颗DDR4的设计。 目前比较常用的

2020-12-21 14:04