电子发烧友

7629次浏览

嵌入式DDR接口原理及设计 有助于SoC设计取得成功的十条建议 DDR3等DRAM标准是由JEDEC开发的。这个组织已经为许多半导体器件制定过标准,而大多数DR

2010-03-13 11:36

本篇主要针对Zynq UltraScale + MPSoC的DDR接口,从硬件设计的角度进行详细介绍,最后展示一下小编之前自己设计的基于ZU+的外挂8颗DDR4的设计。 目前比较常用的

2021-09-16 10:17

我有一个RGMII接口,时钟与边缘的数据DDR对齐。根据我的理解,我应该使用具有90°相位的再生时钟来采样具有最佳时序余量。这意味着我必须使用一个PLL我看到用于DDR接口

2019-03-12 09:56

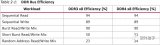

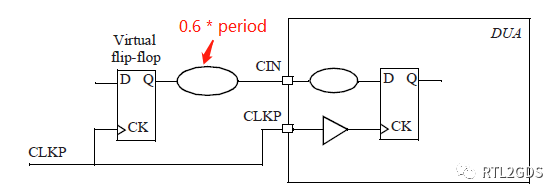

IO约束在顶层和模块级的主要命令都是以下几个,但是实际应用的复杂程度不可同日而语,本篇会先介绍模块级IO约束实战经验,然后讲解顶层IO约束复杂性,过程中会介绍DDR接口时序。

2023-06-27 15:07

大家好,我开发了DDR2内存和高速ADC 500Mpbs(2 ADC)到Spartan6 LX25器件。我想知道银行分配的最佳选择,因为接口都是高速且需要时钟定时至关重要。根据MIG的推荐,DDR

2019-07-12 06:30

随着航天技术的发展,FPGA 等大规模逻辑器件越来越成为不可缺的角色。

2018-08-02 17:41

请问C6457能否用EMIF的DDR2 连接DDR接口的高速AD转换器(ADS62P49)?

2018-07-25 06:28

DDR接口速率越来越高,每一代产品都在挑战工艺的极限,对DDR PHY的训练要求也越来越严格。本文从新锐IP企业芯耀辉的角度,谈谈DDR PHY训练所面临的挑战,介绍芯

2024-01-05 10:27

DDR3的理论带宽怎么计算?用xilinx的控制器输入时钟200M。fpga与DDR的接口如下:

2016-02-17 18:17