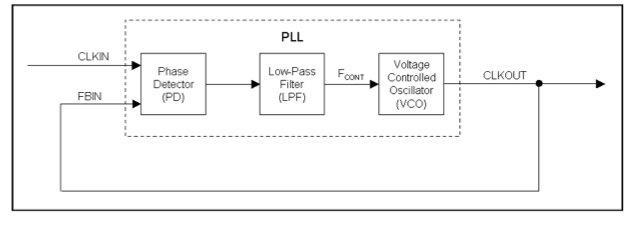

下面我们来看本实例如何配置一个PLL硬核IP,并将其集成到工程中。如图8.18所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Mana

2018-04-24 11:30

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

无任是用CPU作为系统的主要器件,还是用FPGA作为系统的主要器件,系统设计中首先要考虑到的问题就是处理器的启动加载问题。

2017-02-11 19:01

SWM系列关于UART/CAN/PLL等时钟相关模块,计算波特率的方法。

2022-03-18 16:52

在电子系统设计中,无任是用CPU作为系统的主要器件,还是用FPGA作为系统的主要器件,系统设计中首先要考虑到的问题就是处理器的启动加载问题。

2018-07-12 08:27

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14

Altera的Cyclone V FPGA目前是业界系统总成本和功耗最低的FPGA,那我们该怎样为自己的设计选择Altera Cyclone V FPGA?参考本文...

2013-02-26 10:34

本应用报告介绍了实现 IDT 基于 PLL 的零延迟缓冲器的输入参考时钟和输出时钟之间定义的相位关系的不同方法。该报告重点介绍了 PLL 反馈环路中不同走线长度和反馈时

2021-06-15 10:48

广义的来说,FPGA的配置包括直接使用下载电缆对FPGA器件进行编程、对外部EEPROM和FLASH进行编程、使用MPU对FPGA器件进行编程、外部EEPROM和FLASH对器

2016-10-26 10:58

采用新的低成本Cyclone? III FPGA 系列很容易处理这些问题。设计人员可以在Cyclone III FPGA 中应用图像处理算法,转换数字视频信号并映射至显示屏。而且,设计人员还可

2018-09-14 15:52