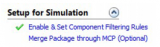

本节介绍Cadence® Sigrity™ 2017 QIR2版本中XtractIM™的新增功能。在该版本中,去耦电容的引脚信息被添加到由XtractIM生成的SPICE模型的MCPheader中。

2018-04-20 08:55

美国Cadence公司近日宣布发布Cadence Sigrity 2018版本,该版本包含最新的3D解决方案,帮助PCB设计团队缩短设计周期的同时实现设计成本和性能的最优化。 独有的3D设计及分析

2018-07-25 17:59

目标阻抗检查是评判PDN性能pass/fail的极好指标。除了已经执行的连续曲线检查之外,OptimizePI还增加了在特定频率点报告阻抗结果的功能。这些频率点是在HTML报告选项窗口中定义的,如下所示。

2018-04-28 15:28

EDA 领域需要运用许多不同的运算软件,然而 EDA 行业所面临的挑战在于,设计团队总需要采用当前的处理器来设计及创建下一代的 SoC。 在 1990 年代和 2000 年代,微处理器公司将处理器的性能每年提高了约 50% 来解决这个问题。部分原因是摩尔定律在没有产生功耗问题的同时,提高了硅芯片的性能;还有部分原因来自于处理器架构的提升,可以通过更聪明的方法来执行乱序执行(Out-of-order Execution)、分支预测(Branch Prediction)以及解决所有其他设计上遭遇

2021-04-08 11:41

Cadence 17.4后 将ORCAD与ALLEGRO的联系更加紧密,同时PCB仿真功能有明显的提升,以前PCB的后仿真基本是在Cadence Sigrity中完成。

2024-02-26 09:12

2017年2月7日,中国上海 —— 楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日正式发布全新Sigrity 2017技术的系列产品,新增多项核心功能,专为加速PCB电源及信号

2017-02-07 15:39

仿真软件识别导入的设计文档是有区别的,实际的使用经历,ADS只是用于搭建Channel通道仿真,那本文以Cadence的Sigrity和Ansys的SIwave为例,讲讲仿真软件的文件导入。

2023-06-10 10:15

新一代Sigrity可以与Clarity 3D Solver场求解器同步运行,并与Cadence Allegro® PCB Designer设计工具和Allegro Package Designer Plus封装设计工具紧密集成。

2021-03-17 11:33

(Virtuoso系统设计平台),结合Cadence Virtuoso平台与Allegro® 及Sigrity™技术,打造一个正式的、优化的自动协同设计与验证流程。

2017-06-13 14:26

电子设计工程师每天都面临着多物理、多领域的设计挑战。当信号完整性、电源完整性和电磁干扰问题被单独处理而不是作为统一系统加以处理时,这些挑战更会加剧。Cadence认识到系统级分析的必要性,为此推出

2022-07-02 14:26 深圳(耀创)电子科技有限公司 企业号