/prdy或者valid-ready或AXI)中Valid及data打拍技巧 ;只关心ready时序修复可以参考同作者这篇文章链接: (

2025-03-08 17:10

由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

2019-05-12 09:10

由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

2022-08-02 12:42

学习内容 学习关于AXI总线的信号接口的具体要求(包括不同通道之间的关系,握手机制说明等)和AXI4-Lite的相关信息,在文章后半部分对AXI读写时序进行了简要讲解,

2021-04-30 11:22

学习内容 学习关于AXI总线的信号接口的具体要求(包括不同通道之间的关系,握手机制说明等)和AXI4-Lite的相关信息,在文章后半部分对AXI读写时序进行了简要讲解,

2021-06-01 10:57

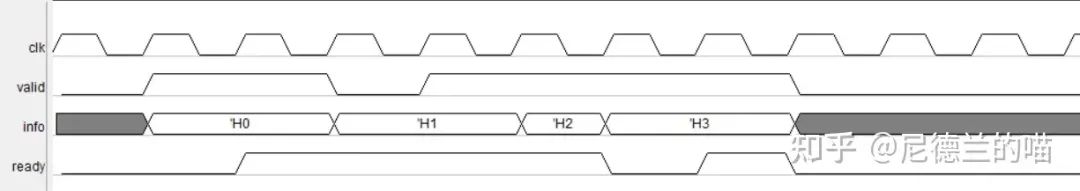

AXI4 协议定义了五个不同的通道,如 AXI 通道中所述。所有这些通道共享基于 VALID 和 READY 信号的相同握手机制

2023-05-08 11:37

4和AXi4-stream都支持三种握手机制,但其具体的总线结构是不同的,详情在后文中会介绍。这三种握手机制分别是:(1) VALID 先变高 READY 后变高。时序图如下:上图中的模式为VALID信号先于

2022-04-08 10:45

start_slave();之后产生slave时序,也可以通过slave的wr_driver或rd_driver,自定义ready的高低电平周期。下图代码展示的是为axi产生自定义wready、awready

2022-10-09 16:08

"Valid-Ready" 握手协议是一种常用于数字电路中的接口协议,用于控制数据的传输和处理。

2023-12-04 10:37

_aw_vid; wirem_axi_aw_ready; wire[2:0]m_axi_aw_port; wire[32-1:0]m_axi_w_data; wirem_axi

2025-07-16 18:50