产生毛刺,且易受环境的影响,不利于器件的移植; 同步电路 1. 电路的核心逻辑是由各种各样的触发器实现的,所以比较容易使用寄存器的异步复位/置位端,以使整个电路有一个确定的初始状态; 2. 整个电路是由时钟沿驱动的; 3. 以触发器为主体的同步时序电

2020-12-05 11:53

CDC(不同时钟之间传数据)问题是ASIC/FPGA设计中最头疼的问题。CDC本身又分为同步时钟域和异步时钟域。这里要注意,同步时钟域是指时钟频率和相位具有一定关系的时钟域,并非一定只有频率和相位相同的时钟才是同步时钟域。异

2022-05-12 15:29

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的

2022-03-09 16:29

本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,

2022-12-13 11:20

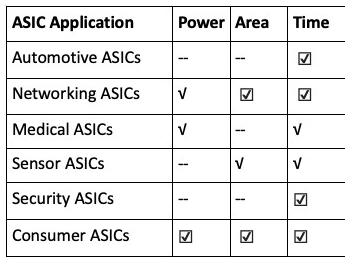

ASIC,如名称所定义,是为特定应用而设计的。可以使用不同的技术来创建ASIC,但由于高可靠性和低成本,CMOS很常见。对于ASIC(SoC设计),功耗、性能(时间)和面积是设计

2022-11-23 16:09

建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2024-08-06 11:40

时序问题跟代码风格本身、资源使用情况等都有关系,代码本身占很大部分,比较复杂的逻辑由于代码没写好,导致最终出现时序问题的情况比比皆是,这就需要多积累多练习,后续我还会持续分享时序方面自己的心得。

2022-09-06 09:27

最后总结一下1,异步通信是面向字符的通信,而同步通信是面向比特的通信。2,异步通信的单位是字符而同步通信的单位是桢。3,异步通信通过字符起止的开始和停止码抓住再同步的机会,而同步通信则是以数据

2018-02-23 08:53

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速

2018-06-07 02:46