在一个SOC设计中,存在多个、独立的时钟,这已经是一件很平常的事情了。大多数的SOC器件都具有很多个接口,各个接口标准都可能会使用完全不同的时钟频率。

2017-02-11 15:07

对于逻辑N而言,由clka产生数据,clkc采样数据,在它们周期的最小公倍数内,最严格的时序是3ns产生数据,在4ns采样。只要保证最严格的情形下,电路正常工作,其他时候都没问题

2023-04-06 11:30

NovaThor L9540是意法爱立信公布的一款高性能的智能手机和平板电脑芯片,最先进的应用处理器相结合的LTE / HSPA / TD-SCDMA多模调制解调器平台解决方案。该平台采用了双核CPU,具有强大的

2012-08-28 15:59

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2020-09-24 10:20

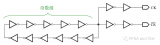

我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。

2023-04-06 10:56

双沿时钟使得原本一个周期输出/输入一个数据的架构,改变为一个周期输出/输入两个数据,这样在不升高时钟频率的前提下,提升了信号的吞吐率,从而带来「性能的提升」。

2023-08-05 09:50

SPICE是一种用于模拟和分析电子电路的计算机程序。在SPICE仿真中,产生时钟信号是许多电路设计和模拟任务中的关键步骤。

2024-02-06 14:22

STM32的定时器除了基本定时器TIM6和TIM7之外,其他的定时器都可以用来产生PWM输出,其中高级定时器TIM1和TIM8可以同时产生7路的PWM输出,而通用定时器

2018-12-13 16:27

时钟域clock domain:以寄存器捕获的时钟来划分时钟域。 单时钟域single clock domain,数据发送和接收是同一个

2022-08-29 15:11

STM32中有多达8个定时器,其中TIM1和TIM8是能够产生三对PWM互补输出的高级定时器,常用于三相电机的驱动,它们的时钟由APB2的输出产生。其它6个为普通定时器

2018-09-03 17:14