本文以高度集成的解调器和频率合成器 ADRF6820 为例,告诉大家如何手动选择频段以

2020-09-01 11:34

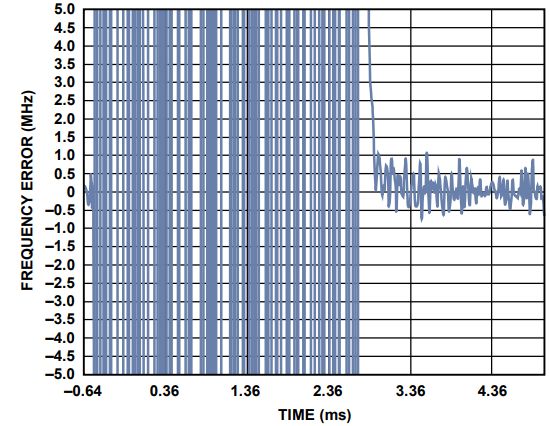

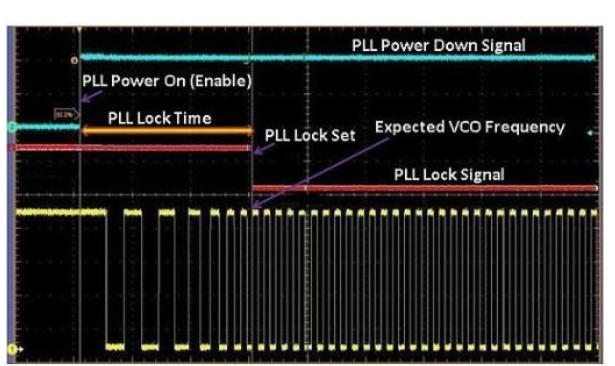

使用自动校准模式时,总锁定时间对某些应用来说可能太长。 本应用笔记提出一种通过手动选择频段来显著缩短

2021-06-21 09:53

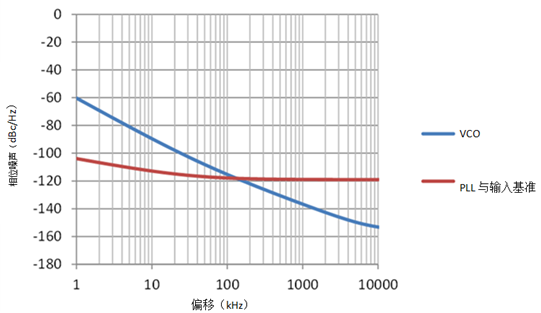

ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于高级通信系统。 它内置一个宽带I/Q解调器、一个小数N/整数N分频锁相环(PLL)以及一个低相位噪声多核压控振荡器(VCO)。

2022-08-09 11:23

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的

2018-03-14 15:17

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO

2018-05-11 15:14

作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳

2016-07-18 14:24

本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率合成器为例,详细介绍了设计过

2023-10-26 15:30

PLL锁定有那些检测方法,它们特点是什么?一种是最为简单的数字检测,它利用输入参考的分频信号与VCO反馈的分频信号,在PFD里鉴相的结果,通过连续结果时钟周期检测到鉴相的脉宽小于某值,作为锁定的有效判决规则。这种检测

2018-03-14 16:37

哈希锁定模式是指用户在规定的时间段对于哈希值的原值进行猜测来支付的一种机制。简单讲,就是在智能合约的基础上,双方先锁定资产,如果都在有限的时间内输入正确哈希值的原值,即

2019-09-10 10:56

在Vivado Implementation阶段,有时是有必要分析一下什么原因导致运行时间(runtime)过长,从而找到一些方法来缩短运行时间。

2019-05-29 14:37