本文旨在提供发生 JESD204B 链路中断情况下的调试技巧简介

2023-07-10 16:32

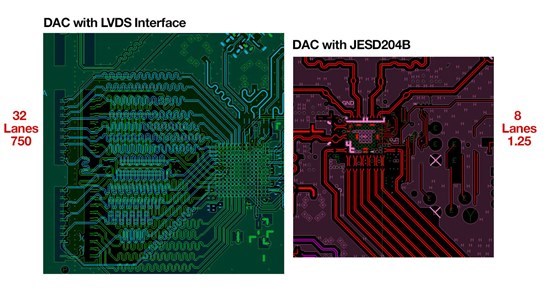

JESD204B IP核作为接收端时,单独使用,作为发送端时,可以单独使用,也可以配合JESD204b phy使用。 JESD204B通常配合AD或DA使用,替代LVDS,提供更高的通讯速率,抗干扰

2024-12-18 11:31

JESD204B接口一般用在高速的AD和DA芯片上,用于传输采集到的数据。该接口相比LVDS可以减少大量的IO管脚,所以正在逐步取代LVDS接口(引用wp446-jesd204b.pdf)。

2022-12-22 09:45

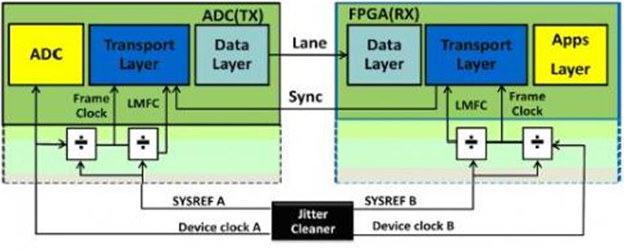

在从事高速数据撷取设计时使用FPGA的人大概都听过新JEDEC标准「JESD204B」的名号。近期许多工程师均联络德州仪器,希望进一步了解 JESD204B 接口,包括与FPGA如何互动、JESD204B如何让他们的

2017-11-18 02:57

本设计致力于用SystemC语言建立JESD024B的协议标准模型,描述JESD204B的所有行为,并且能够保证用户可以通过该JESD204B的SystemC库,进行JESD2

2017-11-17 09:36

在使用我们的最新模数转换器 (ADC) 和数模转换器 (DAC) 设计系统时,我已知道了很多有关 JESD204B 接口标准的信息,这些器件使用该协议与 FPGA 通信。此外,我还在 E2E 上的该

2017-04-08 04:48

明德扬的JESD204B采集卡项目综合上板后,可以使用上位机通过千兆网来配置AD9144和AD9516板卡,实现高速ad采集。最终可以在示波器和上位机上采集到设定频率的正弦波。本文重点介绍JESD204B时钟网络。

2022-07-07 08:58

JESD204B规范是JEDEC标准发布的较新版本,适用于数据转换器和逻辑器件。如果您正在使用FPGA进行高速数据采集设计,您会听到新的流行词“JESD204B”。与LVDS和CMOS接口相比,这一较新的版本具有显著的优势,因为它包括更简单的布局和更少的引脚数。

2023-05-26 14:49

Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx® Inc., 7系列FPGA及Zynq®-7000全可编程SoC。

2013-10-17 16:35

作者:Sureena Gupta 如果您有接触使用 FPGA 的高速数据采集设计,没准听说过新术语“JESD204B”。 我在工作中看到过很多工程师询问有关 JESD204B 接口的信息以及它

2021-11-10 09:43