在高速数据采集系统中,AD芯片的工作速度通常是很高的,可以达到几兆甚至几十兆,而微控制器MCU的工作速度相对较低,并且其往往具有多个任务,所以不能采用AD转换一次MCU读取一次数据的工作方式。

2019-12-03 16:00

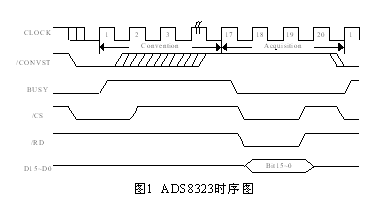

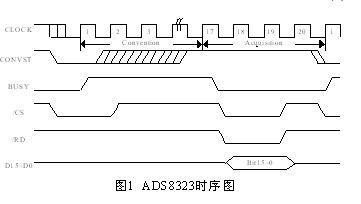

ADS8323需要外接时钟信号,时钟频率范围从25kHZ(1.25kSPS)到10MHZ(500kSPS),其内部的所有动作均与时钟信号同步。工作过程如下:将/CONVST置成低,即可启动转换;在

2019-01-22 16:13

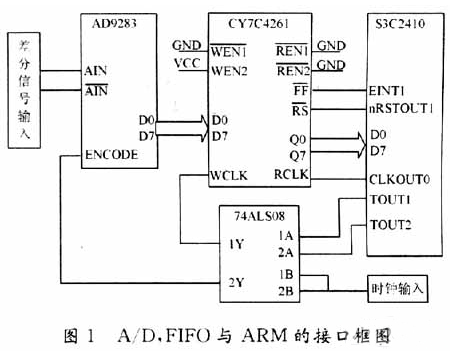

在高频超声波数据采集系统中,很多高速A/D转换器往往不能直接与处理器相连接,这时就需要使用FIFO在处理器与A/D转换器之间架一座桥梁,FIFO的先入先出特性可以方便缓存大量的数据块。

2019-11-05 15:54

摘要: 设计了一组基于CPLD的PLC背板总线协议接口芯片,协议芯片可以区分PLC的背板总线的周期性数据和非周期性数据。详细介绍了通过Verilog HDL语言设计状态机、协议帧控制器、FIFO控

2012-07-05 11:18

本文设计了一种基于CPLD(复杂可编程逻辑器件)+FX2(单片机CY7C68013)的便携式高速数据采集系统,采用了数据流驱动多模块并行技术和USB2.0接口。实践证明,该方案结构简单,成本低廉

2012-05-25 09:53

采用CPLD与绝对式编码器进行高速串行通信,CPLD再把收到的编码器信息转变为并行数据传送给伺服单元中的DSP进行运算控制,本文将给出CPLD与绝对式编码器

2011-08-13 14:57

ADS被越来越多的工程师用于高速电路的信号完整性当中,ADS其中的一个特点就是对模型兼容性非常好,当然ADS也包含了非常丰富的模型。

2018-07-17 15:26

。本文阐述从分立逻辑器件测量炮口初速改装为应用CPLD测量炮速,提高了测量系统的集成度,且传输接口采用的是目前流行的串行高速数据传输接口USB 2.O

2020-04-11 10:08

在ADS中搭建好S参数无源链路原理图,并设置好各项参数,尤其是S仿真器频率、起始频率和步长。

2019-01-01 09:26

上集成的高速FIFO实现采集数据的高速缓存并通过对高速FIFO的读写操作实现总线同步数据传输,提高数据的传输速率。

2018-07-12 09:06