的扇出型缓冲器,是一种将一路时钟源信号通过频率复制生成多路时钟信号的器件,通常时

2022-10-18 18:36

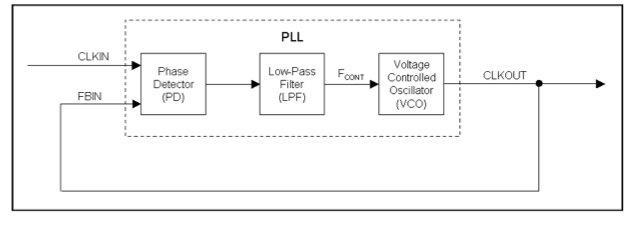

本应用报告介绍了实现 IDT 基于 PLL 的零延迟缓冲器的输入参考时钟和输出时钟之间定义的相位关系的不同方法。该报告重点介绍了 PLL 反馈环路中不同走线长度和反馈

2021-06-15 10:48

三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态

2018-01-11 10:42

HMC7043是一种高性能时钟缓冲器,用于为具有并行或串行(JESD204B型)接口的高速数据转换器分配超低相位噪声参考。

2023-05-31 10:47

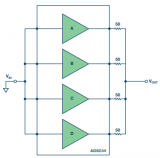

想要降低系统中增加的噪声,必须降低电压噪声。常用方法——并联放置多个缓冲器可降低电压噪声。但是,该方法会使偏置电流、电流噪声、输入电容,统统提高,这时,你需要一款4通道JFET缓冲放大器! 缓冲器是什么? 许多电子电

2018-05-27 05:13

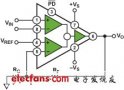

本文讨论了将低失真、低噪声、高速放大器用作DAC缓冲器的一些优势,并将其性能与变压器进行了比较.同时比较了采用两种不同架构的三类应用电路

2012-06-13 11:17

速度差距的存储装置叫做缓冲器。把数据存放到缓冲器中的技术叫做缓冲。 比如缓冲寄存

2022-10-18 19:01

阻抗, ZIN是接收器的输入阻抗。 PS:这里仅显示CMOS和PECL/LVPECL电路。 串行端接 实际上,因为阻抗会随频率动态变化,难以达到阻抗匹配,所以缓冲器输出

2019-11-11 15:55

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟

2023-06-08 15:29

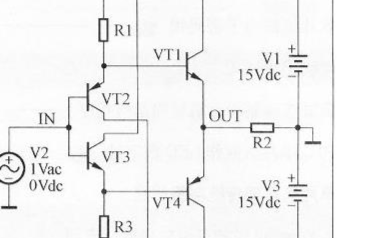

MAX13256具有可调过流门限,用于短路保护。不幸的是,这个阈值使得使用标准方法为设备设计缓冲器变得困难。本应用笔记介绍了如何为MAX13256设计电压缓冲器,同时考虑限流特性。

2023-06-25 14:22