刚刚学完STM32 ADC,在自己写程序的时候发现了一个问题,就是配置PCLK2时钟的时候,分别有2 4 6 8的分频,但是手册上说ADC最大就14MHz,那么我就想问如果配置

2018-09-29 10:07

请问一下,stm32H743使用ADC中断,采集速率是不是和中断源的分频没有关系呀,我是用的是hsi作为时钟源,因为PLL2不知为何我的芯片使用不上,然后我发现无论我怎么改adc的时钟

2024-03-11 07:48

(即使把ADC的分频系数设置成1/4系统时钟,采集的数据以下曲线也是差不多的)。各位大侠请帮忙分析下是什么原因造成的。file:///D:/Program%20Files/Netease/%E7%BD

2018-11-02 08:49

是对的 ,这个会影响到定时器的精度和ADC的分频 (ADC最高50Mhz)。手上有2片HPM6360IP A2 刚打样 。

2023-06-13 07:13

电子发烧友网站提供《STM32G4中ADC触发分频的实现方式.pdf》资料免费下载

2023-09-19 16:38

); RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1, ENABLE ); RCC_ADCCLKConfig(RCC_PCLK2_Div8);//ADC分频 最大14M96

2022-05-25 06:36

从分频方式看可以分为两种,一种是主动分频(PassiveCrossover),或者叫电子分频,也可以叫外置分频、有源分频

2019-10-08 10:37

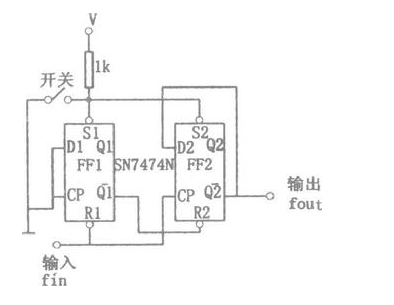

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整数

2023-03-29 11:38

ADC模块中包含一个预分频器的ADC时钟源,它可以对大于100KHz的系统时钟进行分频,以获得合适的ADC时钟提供

2015-11-02 17:45

分频系数可变的分频器

2009-04-11 10:18