AD9361 lvds模式接口。之前用ad9361时至调试了cmos接口,现在调试一下lvds模式。接口模式 : 2r2t每个通道数据率(40×2×12bit)i/q两

2018-08-30 11:49

我在手册上看到AD9361 LVDS模式发送数据的时钟要使用双边沿,在FPGA中,我将FB_CLK倍频到2倍使用单边沿发送数据,再将FB_CLK不变输出到ad9361,这样可以吗?还是必须在FPGA中直接使用FB_C

2018-10-15 09:21

新手求分析上图时序万分感谢!!!

2014-08-05 16:36

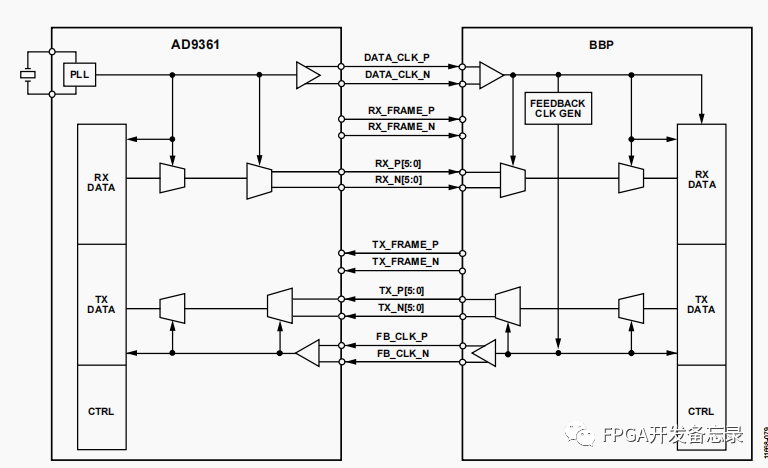

接下来将介绍AD9361数据路径在低电压差分信号(LVDS)模式下运行。AD9361数据接口使用并行总线(P0和P1)在AD9361和BBP之间传输数据样本。

2023-04-25 15:51

AD9361 Datasheet 射频芯片中的佼佼者 性能很好

2016-06-06 10:29

AD9361芯片工作频率范围为70 MHz至6 GHz,涵盖大部分特许执照和免执照频段,通过对AD9361自身可编程改变采样速率、数字滤波器和抽取参数,使该芯片支持的通道带宽范围为低于200 kHz到56 MHz。

2021-03-09 11:47

AD9361是一种宽频带软件可定义收发器芯片,由ADI(Analog Devices Inc.)公司研发,可用于各种射频(RF)应用。它是一种全集成的射频收发器,实现了收发器功能。在这篇文章中,我们

2023-12-26 15:49

我使用ad9361 工作在TDD,lvds模式下;通过enable和txnrx两个管脚控制切换 TDD状态机,使AD9361在alert,Tx,Rx三种状态间切换。现遇到两个问题:1:

2018-12-27 09:43

AD9361:RF捷变收发器

2021-03-19 10:44

,ad9361配置为lvds全双工模式,fdd模式。请问该查看哪些寄存器? 软件配置完芯片后我就将芯片的ensm置于fdd(发射)状态,应该这样做 么?

2019-02-26 10:32