AD7768/AD7768-4允许用户在信号带宽(或动态范围)与功耗之间进行取舍,从而实现更低的功耗,支持更广泛的用途。图4中的动态范围与ODR的关系曲线显示了这种灵活性。

2022-07-26 10:35

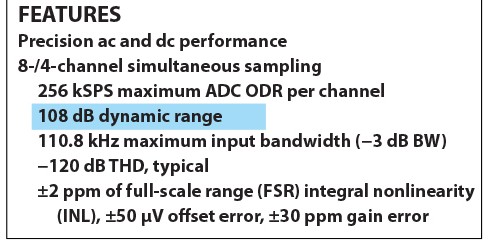

AD7768/AD7768-4分别为每通道集成Σ-Δ型调制器和数字滤波器的8通道和4通道、同步采样Σ-Δ型模数转换器(ADC),支持交流和直流信号的同步采样。

2020-12-03 11:46

AD7768-1 是一款低功率、高性能 Σ-Δ 模数转换器 (ADC) ,其具有一个 Σ-Δ 调制器和数字滤波器,可实现AC 和 DC 信号的精确转换。AD7768-1 是 AD7768 的单通道

2020-12-02 11:54

应用工程师经常会重复回答不同客户提出的相同问题,尤其是客户针对应用进行器件选型相关咨询时。我们注意到客户进行器件选型时有一个误区,他们往往过于依赖数据手册中的所谓“数据表”。我是说令人心动的规格。“哇!那个ADC的信噪比好高!”这就是客户面对高信噪比ADC时的反应,他只注意到这个比较突出的特性,却忘记考虑其他重要的数据规格。接下来我们还会谈到其他常见的问题,以及如何为您的应用选择合适的器件。

2020-07-29 17:17

模拟输入/输出模块设计的共同趋势是以更小的尺寸因数实现更大的通道数。该趋势由通过增加仪器仪表 (PXI) 卡槽的单个模块或PCI扩展可实现的测量值数以减少成本和测试时间的需求所驱动。通道密度的增加导致更多的热消耗,这是模块化应用中设计师面临的共同问题。要使设计满足高密度数据采集模块的热预算要求,客户必须考虑速度、带宽和性能的权衡。

2023-06-16 15:50

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

Verilog HDL是一种用于数字系统设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型也称为模块。Verilog HDL既是一

2019-03-08 14:29

Analog Devices Inc. EV-ADAQ7768-1FMC1Z评估套件用于评估ADAQ7768-1 μModule®数据采集 (DAQ) 系统的功能。 Analog Devices

2025-06-15 14:27

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog测试平台设计方法及

2024-12-17 09:50

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构化编程,代码更直观,易于

2024-12-17 09:44