模拟输入/输出模块设计的共同趋势是以更小的尺寸因数实现更大的通道数。该趋势由通过增加仪器仪表 (PXI) 卡槽的单个模块或PCI扩展可实现的测量值数以减少成本和测试时间的需求所驱动。通道密度的增加导致更多的热消耗,这是模块化应用中设计师面临的共同问题。要使设计满足高密度数据采集模块的热预算要求,客户必须考虑速度、带宽和性能的权衡。

2023-06-16 15:50

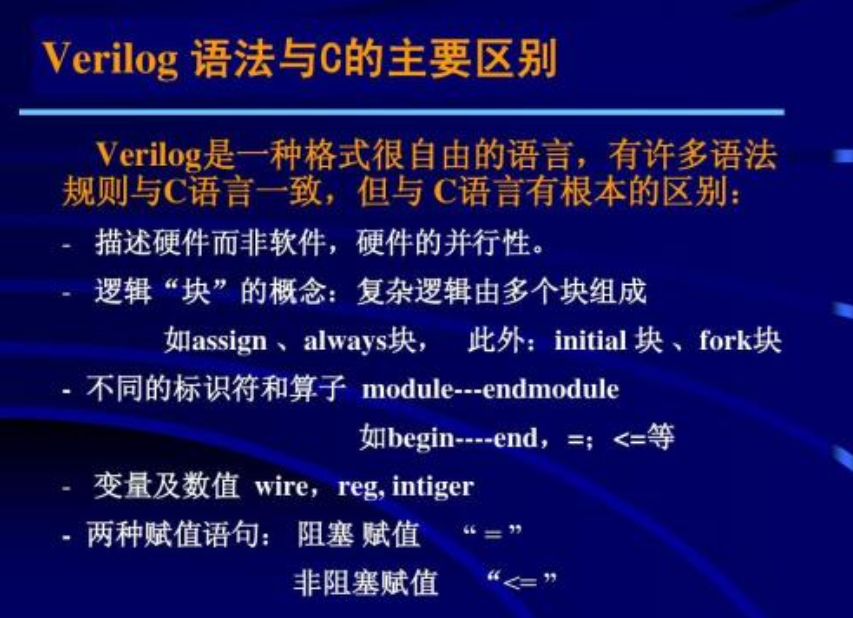

本文首先介绍了verilog的概念和发展历史,其次介绍了verilog的特征与Verilog的逻辑门级描述,最后介绍了Verilog晶体管级描述与

2018-05-14 14:22

Verilog测试平台设计方法是Verilog FPGA开发中的重要环节,它用于验证Verilog设计的正确性和性能。以下是一个详细的Verilog测试平台设计方法及

2024-12-17 09:50

Verilog 与 VHDL 比较 1. 语法和风格 Verilog :Verilog 的语法更接近于 C 语言,对于有 C 语言背景的工程师来说,学习曲线较平缓。它支持结构化编程,代码更直观,易于

2024-12-17 09:44

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52

介绍几种自动生成verilog代码的方法。

2024-11-05 11:45

Verilog模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。 不幸的是,在设计的早期,我们很难把握设计的细节。 而且,一旦模块

2023-06-12 10:05

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

2022-03-15 13:34

学习verilog最重要的不是语法,“因为10%的语法就能完成90%的工作”,verilog语言常用语言就是always@(),if~else,case,assign这几个了。

2018-03-26 14:06

在实际工作中,许多公司对Verilog程序编写规范都有要求。在公司内部统一Verilog程序编写规范不仅可以增强程序的可读性、可移植性,而且也有助于逻辑工程师之间交流、沟通,提升逻辑组成员之间的团队协作能力。本文就大部分公司常见的

2022-09-15 09:35