请问我在PADS使用使用过孔的时候发现从top连到bottom层的时候(4层的板子),中间的层过孔显示的外围的keepout(就是比焊盘大6mil的一圈),但是实际上中间层应该只是一个钻孔(而且

2014-12-08 10:45

它这图片放大显示后有个6mil提示是什么错误呢?

2019-08-08 23:55

请教大家一个问题,对于两层板的LVDS差分对与对之间加6mil地线(由于空间限制),加与不加哪个更好!谢谢大家

2015-02-03 10:23

DRC检查是依据自行设置的规则进行的。例如自己设置的最小间距是8mil,那么实际PCB中,出现小于6mil的间距就会报错。并不是DRC有错误的板子就不能使用,例如丝印的

2019-07-04 09:10

差分对线距规则设置为6mil,是不是因为在clearance中设置最小间隔为10mil就会报错,该怎么解决?一般的差分对线宽,间距都设置多少基本满足一般需求?

2019-05-21 05:35

高速差分信号接到SMA头上时,差分走线必须分开,为了保证阻抗连续性,在分开的拐点处阻抗应该逐渐变小,因此要求走线由6mil变换为8mil。如何将PCB走线由6mi线性变化为8m

2015-06-13 21:29

而且无论把10mil改的如何小总是提示这个错误,有没有大神帮我解答一下

2019-05-23 05:35

用户380674166 问:最快4ns左右上升时间的数据线,走线离过孔应该至少多少mil,线宽5mil,过孔内径6mil?

2014-12-10 10:24

MIL-LT-1/4-4-STK

2024-08-01 22:44

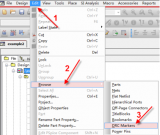

orcad怎么去浏览DRC检测过后的全部DRC错误呢? 答:对原理图文件进行DRC检测以后,按照设置的DRC检测的选项,会在原理图中留下

2021-11-09 11:14