通过Cadence软件建立DDRⅡ信号拓扑结构、仿真信号的串扰、码间干扰、过冲等与信号质量相关的参数,从仿真波形中可以测量出与信号时序相关的参数,从而计算出信号的时序裕量,并为

2012-02-13 15:16

作者:黄刚DDR仿真作为一个非常普遍的仿真模块,基本上入门SI行业的人都会首先接触到。记得本人刚接触这个行业的时候,也是先接触DDR模块的

2019-07-24 06:56

DDR验证是任何SoC中最关键和最复杂的任务之一,因为它涉及位于DUT内部的控制器和位于DUT外部的外部DDR存储器。 DDR系统由控制器,I/O,封装,插座,电源,时钟和外部存储器组成,它们共同

2019-08-12 11:29

DDR仿真作为一个非常普遍的仿真模块,基本上入门SI行业的人都会首先接触到。记得本人刚接触这个行业的时候,也是先接触DDR模块的

2021-03-31 14:01

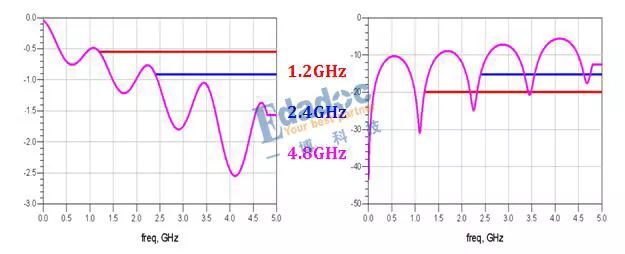

有源的模型这个没什么好说的,就摆在这里,我们也只能管管模型对不对。那我们说说提取链路的无源参数吧。我们以DDR4的数据信号(2400Mbps)为例来说明。

2022-04-07 15:55

不知道现在大家做的DDR4系统的指标是怎么样了?从高速先生和最近众多客户的配合来看,从一个通道的总容量和速率上都基本上拉到了极限,从单个颗粒的容量,很多已经从8Gb提升到了16Gb,运行速率也从typical的2400M拉到3200M了。

2023-12-04 11:20

第一次接触DDR的仿真我也是比较茫然的,首先各种仿真软件基本没有使用过,研究生阶段虽然使用过ADS、HFSS等仿真软件,但主要还是进行无源链路的

2023-02-11 09:59

DDR设计在产品项目中占有举足轻重的地位,俗话说,最小系统设计成功,那项目就已经成功了一大半。

2023-09-26 10:20