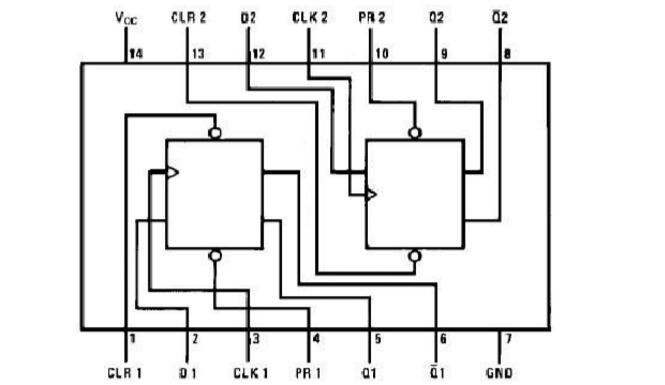

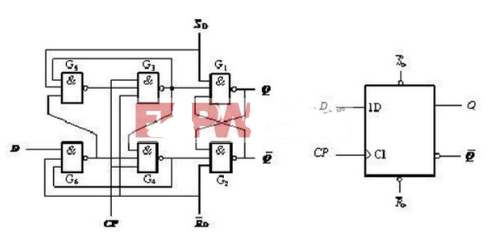

74LS74内含两个独立的D上升沿双d触发器,每个

2021-06-04 15:40

本文首先介绍了74ls74引脚图及功能,其次介绍了边沿D触发器结构与真值表,最后介绍了74ls74的三款应用电路。

2018-04-28 12:42

数字电路中,数字电平从低电平(数字“0”)变为高电平(数字“1”)的那一瞬间叫作上升沿。上升沿触发是当信号有

2018-02-24 17:39

74ls174是六D型触发器。本文首先介绍了74ls174特点和引脚及功能,其次介绍了74ls174典型参数与功能表,最

2018-05-08 11:06

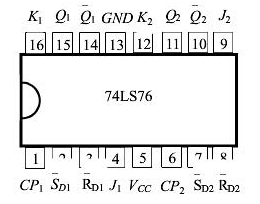

同样值得注意的是,JK 触发器可以通过施加时钟脉冲信号来改变它们的状态。请注意,此时钟信号可以是上升沿或下降沿。此外,74LS

2023-05-05 09:26

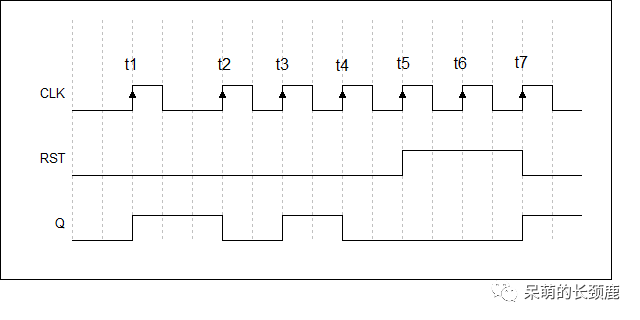

T触发器(Toggle Flip-Flop)Toggle是一个边缘触发的切换触发器,输出Q在输入CLK的每个上升沿时发生

2023-12-04 15:20

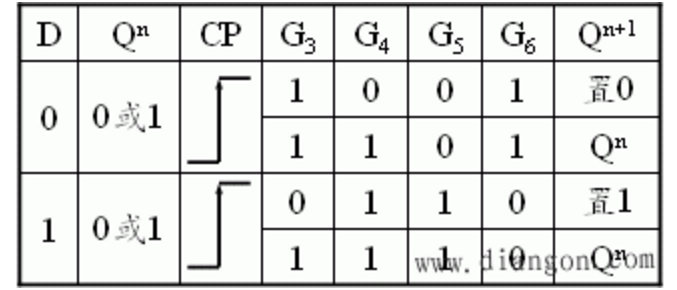

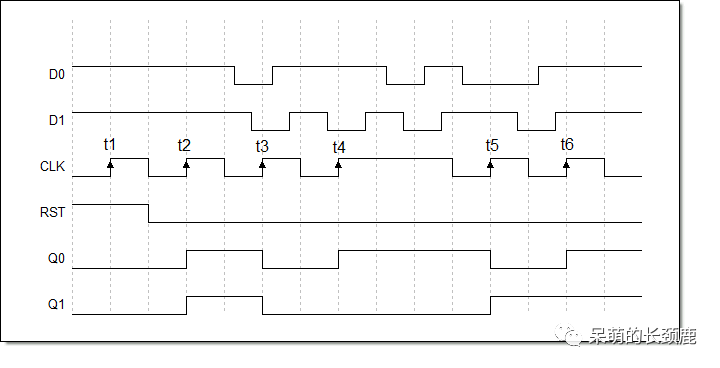

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器

2019-07-12 08:50

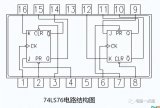

74LS76是双J-K 触发器(负沿触发、带清零和预置)。

2021-07-02 14:23

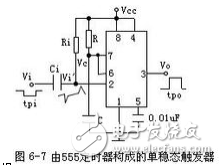

,该暂态维持一段时间又回到原来的稳态,暂稳态维持的时间取决于RC的参数值。常用的单稳态触发器芯片有:74ls121,74ls122,74ls123,CD4098,CD4528,CD4047.

2018-03-28 18:22

D触发器(D Flip-Flop)是一种数字电子电路,用于延迟其输出信号(Q)的状态变化,直到时钟输入信号的下一个上升沿

2023-12-04 15:23