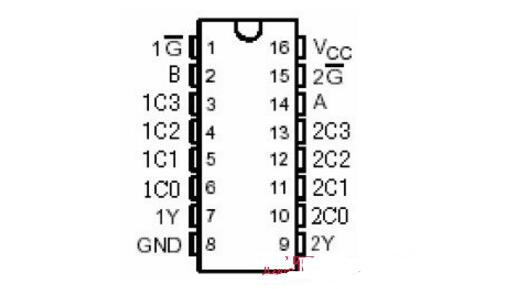

本文介绍了74ls153的管脚图、74ls153功能表、74ls153真值表以及逻辑图,另外还介绍了74ls153封装与74ls

2018-01-26 10:05

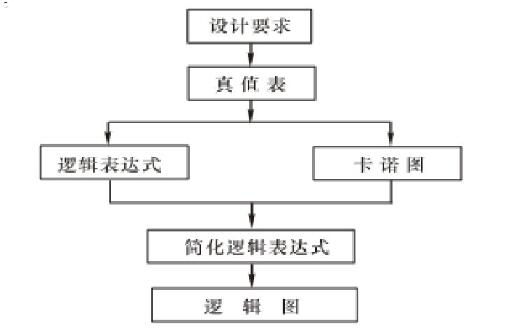

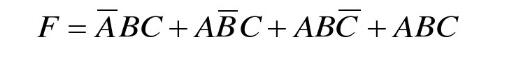

本文介绍了4种方式实现三人表决电路。其中包括用74LS00,74LS20实现三人表决电路、用译码器138和与非门74LS20设计实现三人表决

2018-01-26 17:26

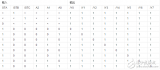

本文主要介绍了用74ls151实现全加器设计电路。根据全加器的定义可知:输入为:A,B,Ci其中A,B为被加数和加数,Ci为低位进位数。输出为:S,Co,其中S为本位和

2018-05-07 09:52

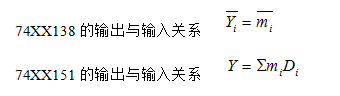

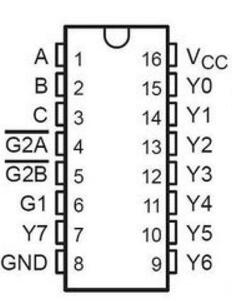

用两片74LS138设计一个全加器。在考虑到74LS138译码器为3 线-8 线译码器,共有 54/74S138和 54/74L

2017-10-31 15:53

本文主要详解四位全加器74ls83,首先介绍了74ls83特点及引脚图、真值表,其次介绍了74ls83功能表、典型参数及

2018-05-31 09:12

本文主要介绍了数据选择器74ls153应用电路图大全(表决电路\交通灯\报警电路)。所谓双4选1数据选择器就是在一块集成

2018-05-07 16:59

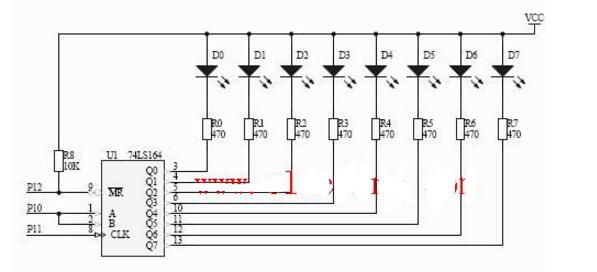

74LS164是一个串行输入并行输出的移位寄存器,可用于扩展并行输出口。74LS165是8位并行输入串行输出移位寄存器,可以扩展一个或多个8位并行I/O口。本文主要介绍

2018-01-27 11:48

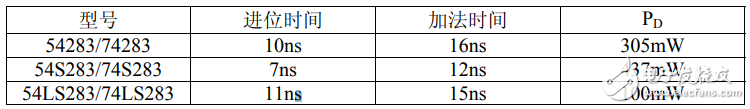

本文主要介绍了74ls283中文资料汇总(74ls259引脚图及功能_逻辑功能及特性)。74ls283是4位二进制超前进位全加器

2018-05-09 15:21

本文主要介绍了74ls151应用电路图大全(全加器\表决器)。五人表决器,只要赞成人数大于或等于三,则表决通过。因此,只需将每位表决人的结果相加,判断结果值。设五个开关A、B、C、D、E作为表决器

2018-05-07 11:38

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

2017-10-31 17:15