74hc138的逻辑功能和74ls138是一样的。74hc138是高速CMOS芯片,工作电源电压为2V - 6V,输出端

2017-10-31 11:19

用两片74LS138设计一个全加器。在考虑到74LS138译码器为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其

2017-10-31 15:53

最近在看逻辑电路,刚刚看到编码器,发现二进制编码器是高电平输入有效,而优先编码器是低电平输入有效,于是就在想,同样都是编码器,为什么不去统一设置一个标准呢?上网搜了搜,

2020-05-18 10:47

推挽输出是低电平还是高电平 推挽输出器是一种常见的输出方式。它由负和正

2023-08-31 10:26

(黄色插头)。这些连接器通常用于连接家庭影院系统、音响设备、游戏机和其他多媒体设备。 关于RCA输出是低电平还是高电平,这实际上是一个关于信号

2024-10-17 11:01

在数字电路中,"clk"通常指的是时钟信号(clock signal),它是一种周期性的信号,用于同步数字电路中的各种操作。时钟信号的高低电平有效性取决于具体的电路设计和应用场景。 1. 时钟信号

2024-07-23 11:24

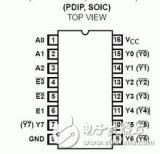

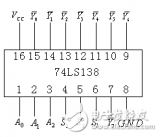

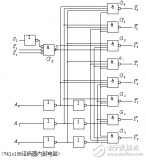

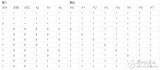

74LS138 为3 线-8线译码器,其引脚图如下。 74LS138引脚功能 A0~A2:地址输入端 STA(E1):选通端 /STB(/E2)、/STC(/E3):选

2017-11-29 19:21

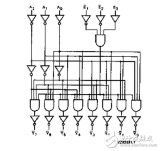

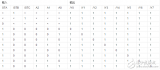

74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(E1)为

2017-12-04 15:48

74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平

2017-10-31 11:44

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为

2017-10-31 16:38