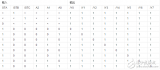

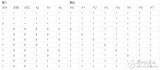

用两片74LS138设计一个全加器。在考虑到74LS138译码器为3 线-8 线译码器,共有 54/74S138和 54/74L

2017-10-31 15:53

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

2017-10-31 17:15

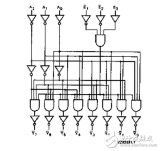

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

2017-10-31 16:38

74hc138的逻辑功能和74ls138是一样的。74hc138是高速CMOS芯片,工作电源电压为2V - 6V,输出端驱动电流为正负25mA。74ls138是TTL芯

2017-10-31 11:19

编写子程序Bin2BCD、BCD2Bin实现二进制数到压缩BCD码的相互转换。待转换的二进制数存放在w寄存器内,子程序调用完成后得到的BCD码仍存放在w寄存器内返回。例如:

2018-05-19 10:59

BCD码亦称二进码十进数或二-十进制代码。用4位二进制数来表示1位十进制

2018-03-14 10:15

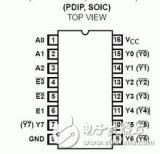

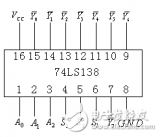

74LS138 为3 线-8线译码器,其引脚图如下。 74LS138引脚功能 A0~A2:地址输入端 STA(E1):选通端 /STB(/E2)、/STC(/E3):选通端(低电平有效) /Y0

2017-11-29 19:21

74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(E1)为高电平,另两个选通端((/E2))和(/E3))为

2017-12-04 15:48

将二进制数视为元胞自动机可能有助于数字二进制计数器的设计和实现吗?

2022-07-28 11:47

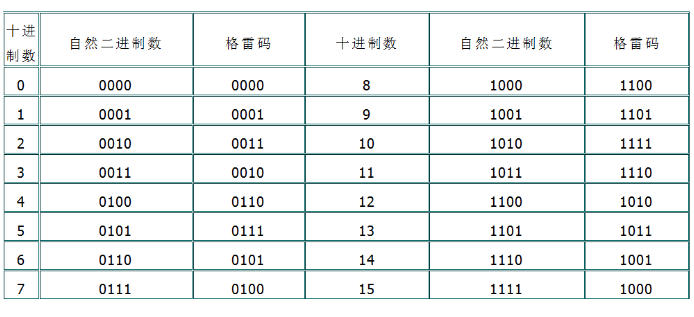

格雷码,又叫循环二进制码或反射二进制码,格雷码是我们在工程中常会遇到的一种编码方式,它的基本的特点就是任意两个相邻的代码只有一位二进制数不同,这点在下面会详细讲解到。格

2018-03-02 15:48