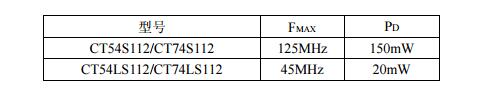

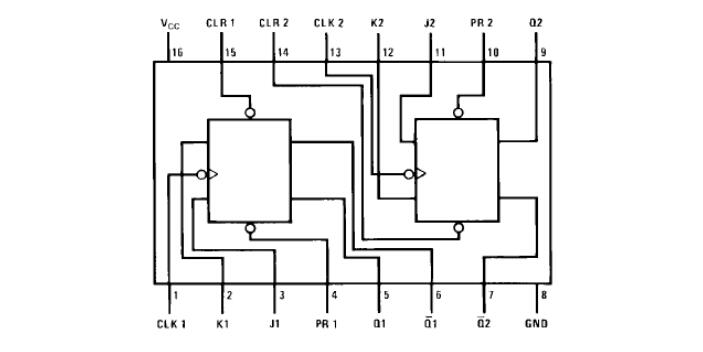

本文首先介绍了74ls112引脚图及功能、74ls112功能表,其次介绍了74ls112极限值及逻辑图,最后介绍了

2018-05-29 18:29

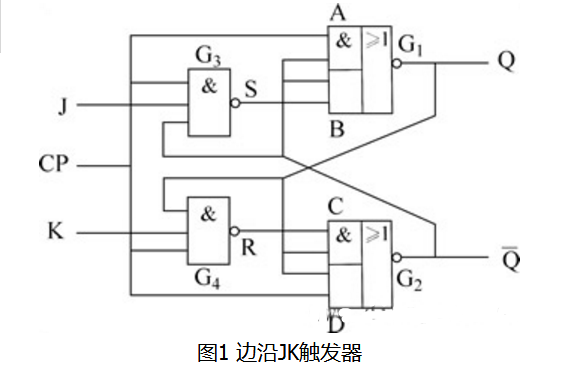

本文开始介绍了JK触发器工作特性与边沿JK触发器的特点,其次介绍了边沿

2018-01-30 17:17

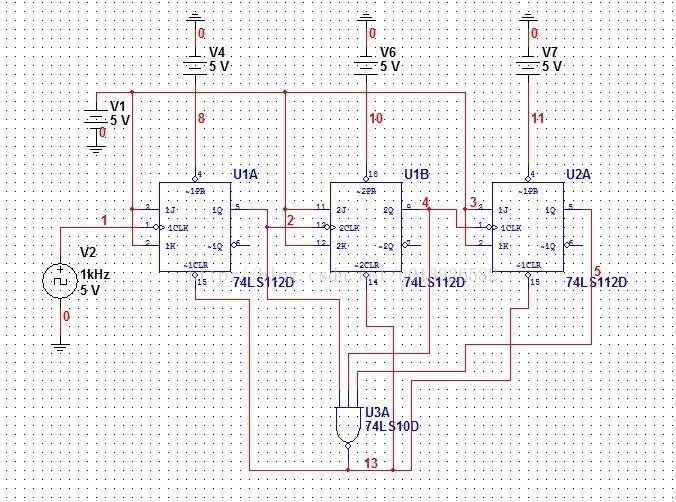

本文主要详解两款74ls112应用电路图,分别是模七计数器/抢答器的电路设计,具体的跟随小编一起来了解一下。

2018-05-29 18:50

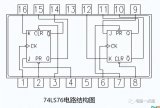

本文开始介绍了74LS112引脚图与74LS112的功能表,其次介绍了74LS76引脚与封装,最后阐述了74LS112和

2018-04-28 14:44

均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。 74ls74双d触发器引脚图 在ttl电路中,比较典型的d

2021-06-04 15:40

边沿触发器只在时钟脉冲CP上升沿或下降沿时刻接收输入信号,电路状态才发生翻转,从而提高了触发器工作的可靠性和抗干扰能力,它没有空翻现象。

2018-01-31 09:17

JK触发器是数字电路触发器中的一种基本电路单元。JK

2019-11-08 14:48

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具

2018-01-31 09:02

rs触发器电路图与rs触发器内部电路图 rs触发器电路图 主从RS

2022-10-19 19:16

同样值得注意的是,JK 触发器可以通过施加时钟脉冲信号来改变它们的状态。请注意,此时钟信号可以是上升沿或下降沿。此外,74LS76 能够忽略无效输出。

2023-05-05 09:26