Borodovsky在采访中表示,另一个可能导致5nm缺陷的因素是现有的EUV光阻剂材料缺乏均匀度。此外,他还表示支持直接电子束写入,因为EUV使用的复杂相移光罩最终将膨胀至目前浸润式光罩价格的8倍。

2018-04-11 15:59

IMEC进行了设计技术协同优化(DTCO),以确定5nm节点上STT-MRAM单元的要求和规格,并得出了一个结论,高性能STT-MRAM位单元的MRAM间距是45nm接触栅极间距的两倍,是5nm最后

2018-12-18 15:33

研究机构IMEC已经发表了一篇论文,该研究表明,在5nm节点上,STT-MRAM与SRAM相比可以为缓存提供节能效果。这种优势比非易失性和较小的空间占用更重要。 半导体行业著名机构IMEC在

2019-04-22 15:51

我们很高兴能在此宣布,Cadence 基于 UCIe 标准封装 IP 已在 Samsung Foundry 的 5nm 汽车工艺上实现首次流片成功。这一里程碑彰显了我们持续提供高性能车规级 IP 解决方案的承诺,可满足新一代汽车电子和高性能计算应用的严格要求。

2025-04-16 10:17

。 GlobalFoundries、英特尔、三星和台积电希望将EUV光刻技术加入到7nm和5nm生产中。但就像以前一样,EUV由几部分组件组成,在芯片制造商能够引入之前

2018-03-31 11:52

现在EUV极紫外光已经提升过一次了。 之前ASML公布的新一代EUV***的量产时间是2024年,不过最新报道称下一代EUV***是2025年量产,这个时间上台积电、三星都已经量产3

2019-07-13 09:40

EUV 光刻是以波长为 10-14nm 的极紫外光作为光源的芯片光刻技术,简单来说,就是以极紫外光作“刀”,对芯片上的晶圆进行雕刻,让芯片上的电路变成人们想要的图案。

2022-10-10 11:15

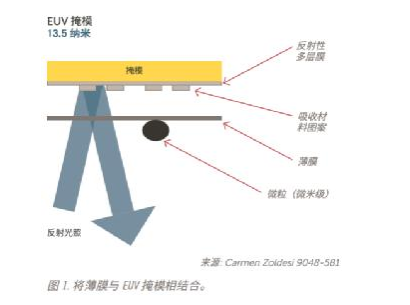

本文简单介绍了极紫外光(EUV)掩膜版的相关知识,包括其构造与作用、清洗中的挑战以及相关解决方案。

2024-12-27 09:26

吞吐量仍然是一个问题,解决方案需要多种技术的结合。事实证明,电子束检测对于发现5纳米以下尺寸的关键缺陷至关重要。现在的挑战是如何加快这一流程,使其在经济上符合晶圆厂的接受度。电子束检测因灵敏度

2025-08-19 13:49 PDF Solutions 企业号

随着半导体行业持续突破设计尺寸不断缩小的极限,极紫外 (EUV) 光刻技术的运用逐渐扩展到大规模生产环境中。对于 7 纳米及更小的高级节点,EUV 光刻技术是一种能够简化图案形成工艺的支持技术。要在如此精细的尺寸下进行可靠制模,超净的掩模必不可少。

2019-07-03 15:32