IMEC进行了设计技术协同优化(DTCO),以确定5nm节点上STT-MRAM单元的要求和规格,并得出了一个结论,高性能STT-MRAM位单元的MRAM间距是45nm接触栅极间距的两倍,是

2018-12-18 15:33

研究机构IMEC已经发表了一篇论文,该研究表明,在5nm节点上,STT-MRAM与SRAM相比可以为缓存提供节能效果。这种优势比非易失性和较小的空间占用更重要。 半导体行业著名机构IMEC在

2019-04-22 15:51

我们很高兴能在此宣布,Cadence 基于 UCIe 标准封装 IP 已在 Samsung Foundry 的 5nm 汽车工艺上实现首次流片成功。这一里程碑彰显了我们持续提供高性能车规级 IP 解决方案的承诺,可满足新一代汽车电子和高性能计算应用的严格要求。

2025-04-16 10:17

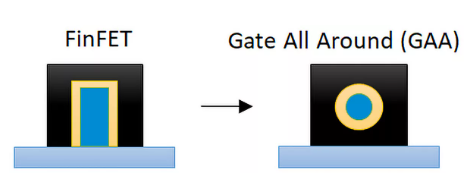

Nandra补充说,“FinFET固有增益很高,但是跨导(gm)实际上很低,和频率(ft)一样。更先进的几何布局比平面器件更容易实现匹配,能够很好的控制晶体管特性。结果

2019-09-25 14:27

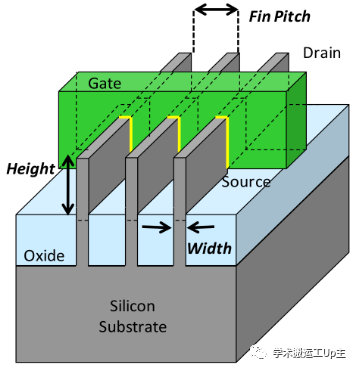

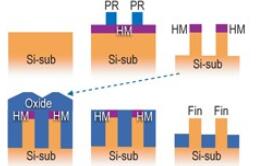

引入不同的气态化学物质进行的,这些化学物质通过与基材反应来改变表面。IC最小特征的形成被称为前端制造工艺(FEOL),本文将集中简要介绍这部分,将按照如下图所示的 22 nm 技术节点制造 FinFET 的工艺流程,解释了 FEOL 制造过程中最重要的工艺步骤。

2023-12-06 18:17

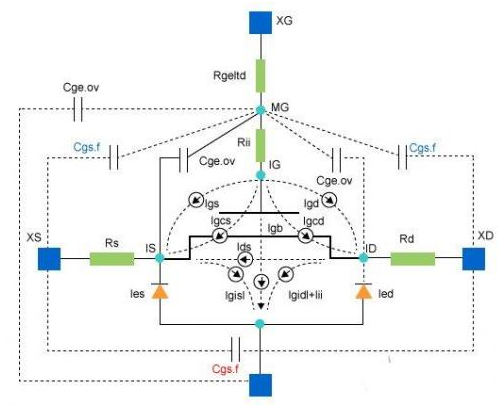

有据可查的是,与平面晶体管相比,从16nm/14nm开始的FinFET技术大大增加了必须提取的寄生值的数量。这些类似3D架构的鳍片会产生许多电容值,必须提取这些电容值才能准确模拟电气行为,并最终

2023-05-25 14:23

前两天,课程群的号友,说他用SystemVue,来仿真链路的级联参数,说遇到问题了。

2023-10-27 15:57

选择电路仿真软件时,哪个更实用主要取决于你的具体需求和偏好。不同的软件在功能、界面设计、操作便利性等方面各有特点。

2024-03-29 14:40

FinFET称为鳍式场效晶体管(FinField-EffectTransistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管。

2017-02-04 10:30

具备雷达探测精度评估、光学探测精度评估、遥测通信质量评估、仿真数据和实测数据比对等多种数据综合评估的能力,可用于完成外界环境影响对测控装备探测精度评估、通信质量评估等场景。

2024-04-26 10:31