h,i,j,k,l,m,n的ascii码值

2009-06-28 11:47

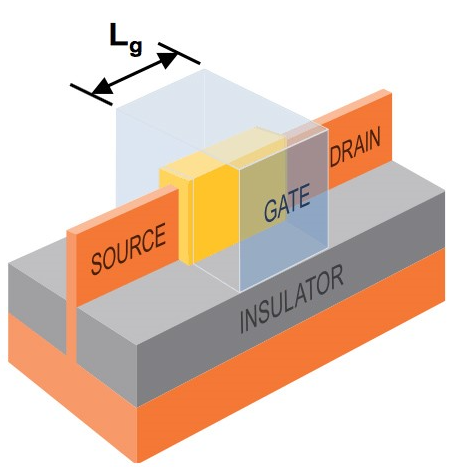

虽然栅极间距(GP)和鳍片间距(FP)的微缩持续为FinFET平台带来更高的性能和更低的功耗,但在5nm及更先进节点上,兼顾寄生电容电阻的控制和实现更高的晶体管性能变得

2022-05-05 16:00

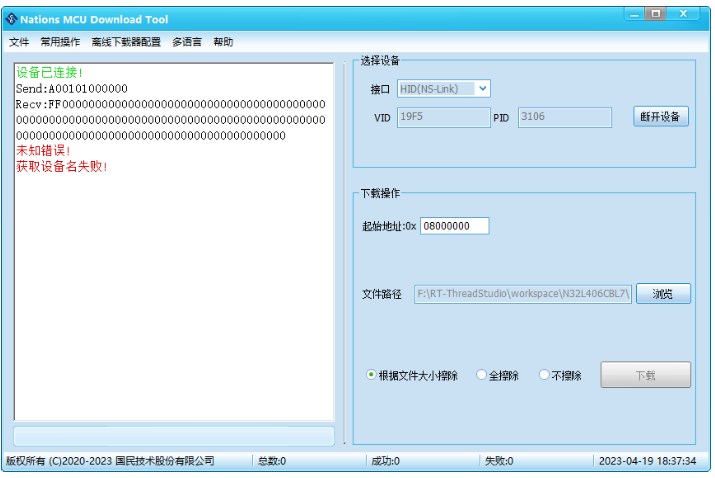

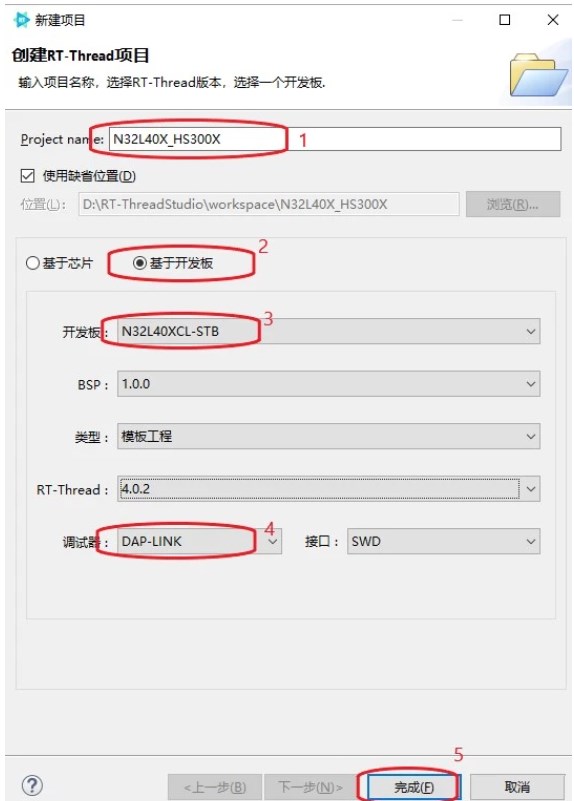

本人基于 rt-thread studio 对 N32L40XCL 进行I2C测试。具体表现为使用 N32L40XCL 的 I2C1 (PA4:

2023-09-18 17:35

虽然栅极间距(GP)和鳍片间距(FP)的微缩持续为FinFET平台带来更高的性能和更低的功耗,但在5nm及更先进节点上,兼顾寄生电容电阻的控制和实现更高的晶体管性能变得

2022-05-07 14:10

32L40XCL集成了2个独立的I2C总线接口,它提供多主机功能,控制所有I2C总线特定的时序

2023-08-11 14:37

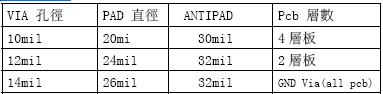

ICT 測試點 LAYOUT 注意事項:pcb layout规则 PCB 的

2008-07-18 12:38

自去年起,台积电和三星等晶圆代工厂纷纷推出了5nm的工艺,如今更是在钻研5nm以下的先进制程。但制程的提升不单单只靠EUV光刻机就能轻易实现的,短沟道效应使得传统的FinFET技术已经满足不了更高

2021-08-19 08:30

电子发烧友网报道(文/周凯扬)自去年起,台积电和三星等晶圆代工厂纷纷推出了5nm的工艺,如今更是在钻研5nm以下的先进制程。但制程的提升不单单只靠EUV光刻机就能轻易实现的,短沟道效应使得传统

2021-08-25 11:02

台积电提到对于包含60%逻辑单元、30% SRAM,以及10%模拟I/O的移动SoC而言,其5nm工艺能够缩减芯片35%-40%的尺寸——这样的值是更具参考价值的。

2021-01-30 11:47

16日,三星电子宣布在基于EUV的高级节点方面取得了重大进展,包括7nm批量生产和6nm客户流片,以及成功完成5nm FinFET工艺的开发。 三星电子宣布其

2019-04-18 15:48