FPGA多数情况下相比ASIC而言,芯片成本大概是100倍的关系,最大的浪费在LUT这里,做出一个LUT-4需要16位存储单元,再加一个4-16译码器,以及其它的连线资

2017-02-11 13:03

本文主要介绍了译码器的分类和应用。译码器指的是具有译码功能的逻辑电路,译码是编码的逆过程,它能将二进制代码翻译成代表某一特定含义的信号(即电路的某种状态),以表示其原来

2018-04-04 11:51

本文首先介绍了译码器的定义与译码器的分类,其次介绍了译码器的作用和译码器的工作原理,最后介绍了译码器的逻辑功能。

2018-02-08 14:04

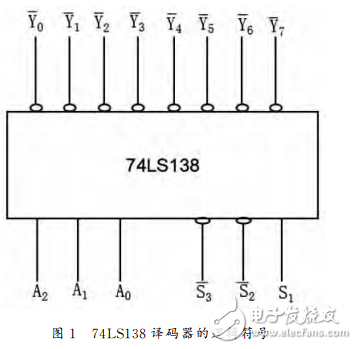

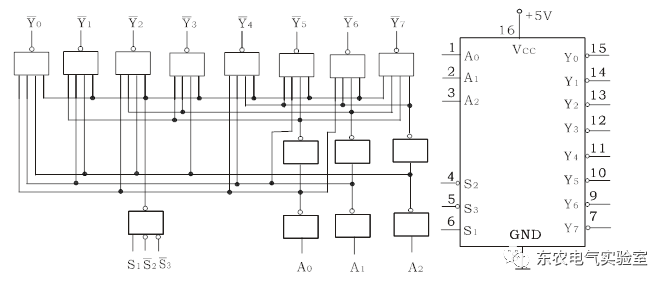

74LS138是带有扩展功能的集成3线—8线译码器,它有3个使能控制端,3个代码输入端,8个信号输出端.控制端用来控制译码器的工作状态,如果仅为了控制译码器,一个使能端就够了,该器件之所以设置三个使能端,除了控制

2017-12-04 16:08

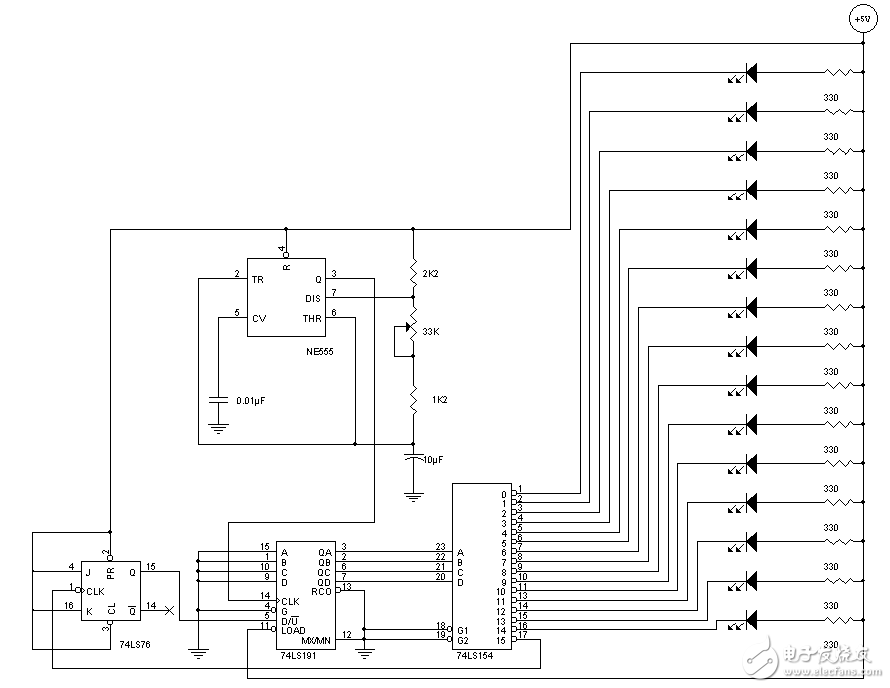

74HC154译码器可接受4位高有效二进制地址输入,并提供16个互斥的低有效输出。

2018-07-19 14:33

该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同

2017-11-22 07:34

译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

2023-10-11 12:51

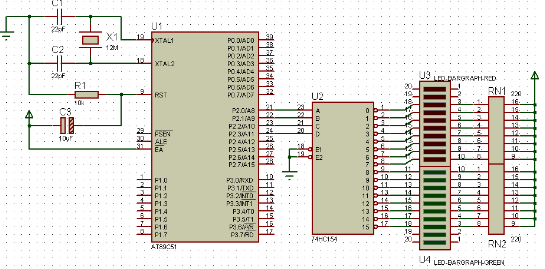

本文主要介绍了74ls154应用电路图大全(LED流水灯\译码器\点阵屏)。重点分析了LED流水灯电路、74LS154译码器的应用程序设计和16x16点阵屏的设计与实现。这种单片

2018-05-08 08:36

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

2018-08-08 09:21

记(n0,k0,m)为卷积码编码器,该编码器共有2k0×m个状态,Viterbi译码器必须具备同样的2k0×m个状态发生器,且每个状态必须有一个存储路径度量值的存储

2020-07-15 20:53