`这样连接可以组成4-16译码器对吧为什么呢原理是什么呢`

2013-11-13 14:48

multisim仿真138构成的4-16 译码器时,当输入为0001时,Y1不灭,但用万用表量电压却是0V,这是为什么?当输入为1111时,Y15和Y1同时灭了, 但用万用表量Y1电压却是5V, 这是为什么?所有连线已重新连接,但还是不行。哪位大神给解答一下。刚学

2020-05-19 19:38

如图,思路是两片74LS138组合形成4-16译码器来实现。但因为不太会用Multisim所以来求助大神

2016-10-20 11:12

求讲下这种级联成4-16译码器的原理

2016-05-09 10:36

就是这个电路,P1的低4位接在两个4-16译码器上,用来扫描4个8*8点阵的阴极,P5、P4用来做

2012-05-16 22:45

4-16译码器74LSl54的工作原理与3-8译码器类似,有4个输入端和16个输出端。锁存

2018-07-26 08:55

FPGA多数情况下相比ASIC而言,芯片成本大概是100倍的关系,最大的浪费在LUT这里,做出一个LUT-4需要16位存储单元,再加一个4-16译码器,以及其它的连线资

2017-02-11 13:03

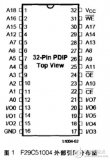

铜板又不给买雕刻机)单片机用的是STC12C5A60S2,兼容51,自带AD蛮好用的。由于是16*16 IO口需要太多,所以用了一个154 4-16译码器!就是板子做的

2013-08-01 10:44

没有办法避免。图3-4 局部放大波形 至此,就完成了一个基本的组合逻辑,3-8译码器的设计。请以此为基础自行设计4-16译码器或者更高位数

2016-12-20 18:54