有据可查的是,与平面晶体管相比,从16nm/14nm开始的FinFET技术大大增加了必须提取的寄生值的数量。这些类似3D架构的鳍片会产生许多电容值,必须提取这些电容值才能准确模拟电气行为,并最终

2023-05-25 14:23

这一集电极电流IC流经电阻RL,从而IC×RL的电压反映在电阻RL两端。最终,输入电压e被转换(增幅)成ICRL电压反映在输出。

2024-04-22 11:46

过去几年,半导体产业风起云涌。一方面,中国半导体异军突起。另一方面,全球产业面临超级周期,加上人工智能等新兴应用的崛起,全球半导体行业竞争激烈。而在芯片代工市场,我们不得不说到台积电、三星和联发科。但目前,台积电占据全球晶圆代工市场大约60%的份额,在7nm工艺节

2019-10-26 11:13

芯片的7nm工艺我们经常能听到,但是7nm是否真的意味着芯片的尺寸只有7nm呢?让我们一起来看看吧!

2023-12-07 11:45

,苹果A17芯片采用了3nm工艺制程,核心参数包括6-core CPU和6-core GPU,为多任务处理提供了强大的支持。 此外,苹果公司的A17芯片的3nm的工艺制

2023-09-26 11:46

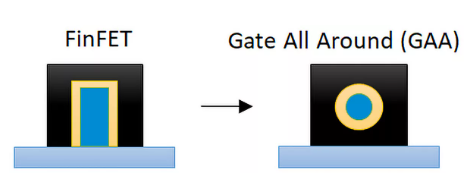

虽然只有12年的历史,但finFET已经走到了尽头。从3nm开始,它们将被环栅 (GAA)取代,预计这将对芯片的设计方式产生重大影响。

2023-04-18 10:05

而且在堆叠层数增加的时候,存储堆栈的高度也在增大,然而每层的厚度却在缩小,以前的32/36层3D NAND的堆栈厚度为2.5μm,层厚度大约70

2018-06-03 09:50

对于薄膜厚度的准确测量,取决于使用什么样的厚度传感器,下面介绍目前在线薄膜厚度的检测技术主要有几种方式。

2019-05-11 11:11

层数的增加也就意味着对工艺、材料的要求会提高,要想达到140层堆叠就必须使用新的基础材料。而且在堆叠层数增加的时候,存储堆栈的高度也在增大,然而每层的厚度却在缩小,以前的32/36层3D NAND

2018-05-28 16:25