本文首先介绍了为什么要使用电子分频器,其次阐述了电子分频器工作原理及作用、特点,最后介绍了电子分频器的调整方法、使用注意事项及发展趋势。

2018-05-24 14:46

本文主要带领大家来了解一下分频器的计算和调整,首先来了解一下分频器原理及是分频点,其次详细了解分频器计算的顺序以及

2018-05-29 09:59

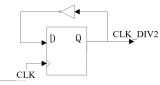

分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他

2023-11-03 15:55

ADI最近发布了一款时钟缓冲器和分频器IC(集成电路)AD9508,该电路结合了高速、极低抖动(12 kHz至20 MHz频段为41 fs)及可选

2013-02-21 11:31

供数字时钟使用的+5000分频器电路

2009-01-13 20:07

缺点:当分频倍数很大时,需要的寄存器也是倍增。当然你也可以采用复用的方式去减少所需寄存器数目,例如,36分频,可以做两个

2018-12-08 10:40

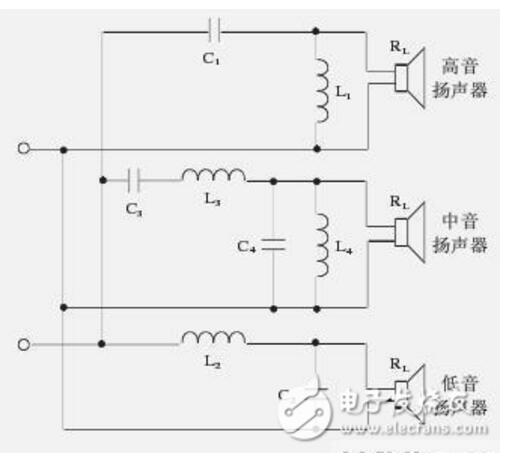

什么是分频器 分频器介绍 分频器是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放

2010-02-05 17:51

时间段就变成了0.5个周期,就不能通过clk的计数直接实现了。 然而,时钟信号的上升沿和下降沿之间正好相差0.5个周期,利用这个就可以实现奇数分频啦 第一步:分别使用原

2021-03-12 15:44

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的

2022-11-21 09:41

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的

2019-02-01 01:49