摘要:提出了一种基于高速锁存器的CMOS高速分频器结构,阐述了其工作速度,工作范围,前后级级联电路设计。采用典型的TSMC0.18Um/1.8V工艺模型,通过Agile

2010-04-30 10:38

文章介绍了采用TSMC 0.18um CMOS工艺设计的2.4GHz WLAN (无线局域网)功率放大器,放大器采用并联拓扑结构设计,改善了功率附加效率(PAE)。在3.3V工作电压下,其压缩点输出功率为21d

2009-06-18 11:17

完整的TSMC 0.18um Mixed Signal SPICE MODEL for Hspice

2009-11-18 10:54

高压0.18um 先进工艺技术上海华虹 NEC 电子有限公司工程一部1、简介项目名称:高压0.18μm 先进工艺技术,该项目产品属于30V 高工作电压的关键尺寸为0.18μm 的逻辑器件。

2009-12-14 11:37

求大佬分享关于TSMC 0.18um dc数字单元的知识点

2021-06-21 07:29

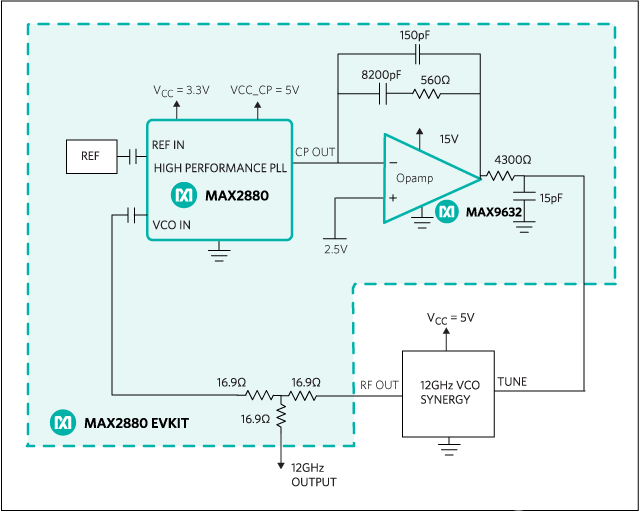

本应用笔记详细介绍了集成外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880)、基于运算放大器的有源环路滤波器(MAX9632)和

2023-01-16 11:27

给出基于0.13μm CMOS工艺、采用单时钟动态负载锁存器设计的四分频器。该四分频器由两级二分频器级联而成,级间采用缓冲电路

2010-12-29 18:00

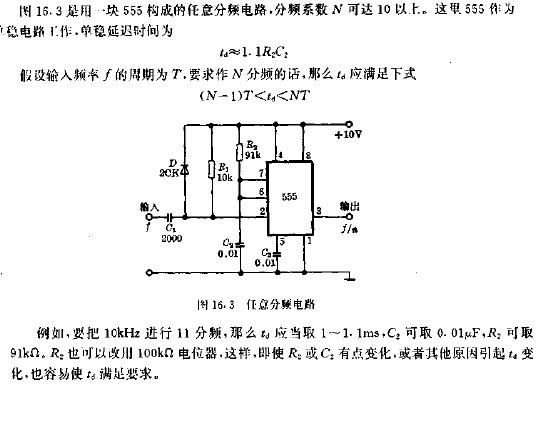

10分频电路 任意分频电路图

2009-06-22 08:04

源三分频电路设计[hide][/hide]

2009-06-22 10:52

本文设计了基于65 nm 工艺的五分频器, 产生一个占空比为50%的五分频信号。对该电路的设计不以追求高速度为惟一目标

2011-11-25 15:07