I2C器件接口IP核的CPLD设计 根据单片机I2C串行扩展的特点,在EDA软件MaxplusII的环境下,利用AHDL语言,建立IP核。此设计利用状态机实现,在给出

2009-03-28 16:21

摘 要: 根据单片机I2C串行扩展的特点,在EDA软件MaxplusII的环境下,利用AHDL语言,建立IP核。此设计利用状态机实现,在给出设计的同时详细说明IP核的建立过程,并下载到

2009-06-20 13:36

高斯滤波的卷积核确定主要依赖于高斯函数的特性以及图像处理的具体需求。以下是确定高斯滤波卷积核的几个关键步骤: 一、确定卷积核的大小 卷积核形状 :高斯滤波的卷积

2024-09-29 09:29

由于CPLD数字设计结构化的趋势,将出现针对CPLD不同层次的IP(Intellectual Property)核。各个IP核可重复利用,可大大提高设计能力和效率。国外各大公司都推出了专门的IP核,我国也迫切需要发展自己的IP

2020-04-07 09:54

目前域控项目有的采用S32G这类多核异构的芯片,转载一篇分析下多核异构中A核与M核通信过程的文章。

2023-10-31 11:09

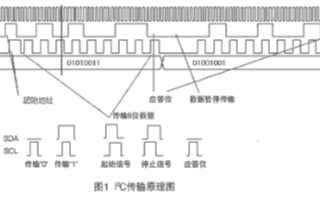

器件都有一个唯一的识别地址,而且都可以作为一个发送器或接收器。当连接在I2C总线上的多个主机器件同时传输数据时,通过仲裁来避免冲突。SDA和SCL都是双向线路,通过一个电流源或上拉电阻连接到电源。器件输出级必须是漏极开路或集电极开路,当总线空闲时,两条线路处于高电

2020-07-20 18:08

送电电压电流核相、测相量及分析

2023-11-17 09:41

NI Multisim 10经典教程分享--电压/电流(U/I)变换电路

2023-01-04 15:22

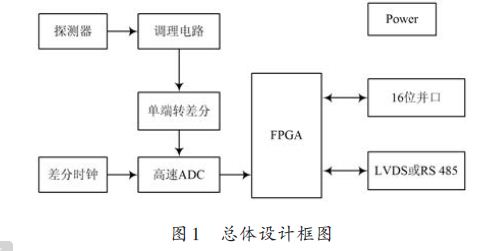

为了研究数字化γ能谱仪,本文提出一种基于FPGA的数字核脉冲分析器硬件设计方案,该方案采用现场可编程逻辑部件(FPGA),完成数字多道脉冲幅度分析仪的硬件设计。用QuartusⅡ软件在FPGA平台上完成了数字

2013-11-21 10:57

多道脉冲幅度分析仪和射线能谱仪是核监测与和技术应用中常用的仪器。##FPGA

2014-06-09 10:42