摘要:本文简要的总结了在高速数字设计中串联终端匹配和并联终端匹配的优缺点

2009-04-15 08:50

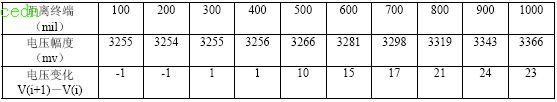

DDR加终端匹配电阻和不加信号质量的区别 DDR(双倍数据传输速率)是一种常用于计算机内存的高速数据传输技术。在DDR中,终端

2023-12-29 13:54

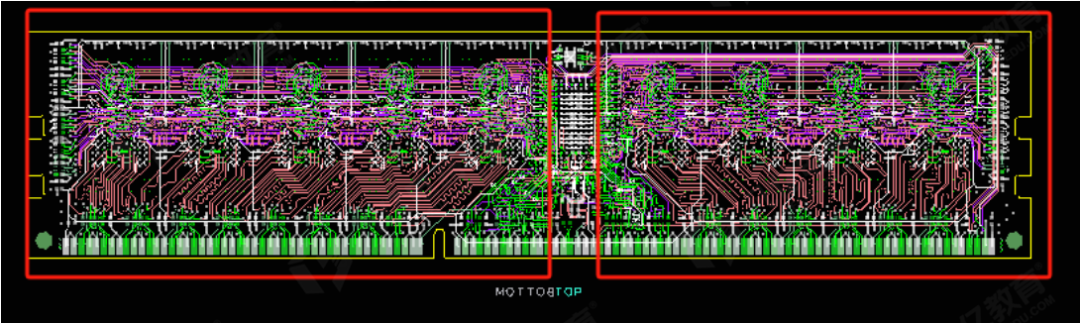

DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行解决,在源端处

2023-12-25 07:45

,只是在谐振电路或者射频电路等特定电路中的叫法。 还有匹配电容,匹配电感等。 匹配电阻的作用 匹配电阻的作用就是是电路稳

2020-12-31 14:28

阻抗匹配阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之则在传输中有能量损失。在高速PCB设计

2014-12-01 10:38

或CMOS电路来说,不可能有十分正确的匹配电阻,只能折中考虑。链状拓扑结构的信号网路不适合使用串联终端匹配,所有的负载必须接到传输线的末端。否则,接到传输线中间的负载接受到的波形就会象图3.2.5

2019-05-29 07:03

电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于 20M的信号PCB走线长度大于5cm时都要加串行

2022-05-16 16:15

电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于 20M的信号PCB走线长度大于5cm时都要加串行

2019-01-02 10:30

阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度成反比。在嵌入式系统中,一般频率大于20M的信号且

2014-07-04 14:00

调整总线的特性阻抗,以确保信号在总线上的传输质量。在485总线中,为了减少信号的反射和保证信号的完整性,通常需要在总线两端接入匹配电阻。匹配电阻的阻值通常为120欧姆,这是由于485总线的标准规定的。 接入

2023-12-20 09:44