使用时钟PLL的源同步系统时序分析一)回顾源

2010-10-05 09:47

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源

2022-12-26 17:04

所示,这样才能保证最充分的建立和保持时间。为了保证选通信号和数据信号相对保持正确的时序,在源同步时钟系统中是通过驱动芯片

2014-12-30 13:54

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源

2019-12-20 07:09

,源同步时钟的并行总线,高速串行总线,如下图所示:[/url]我们先来讨论下绿色的部分,也就是共同时钟的并行总线

2014-10-21 09:35

内同步时钟的时钟信号是从驱动端直接发到接收端的。之前的博文提到,共同时钟系统时序

2019-06-05 14:59

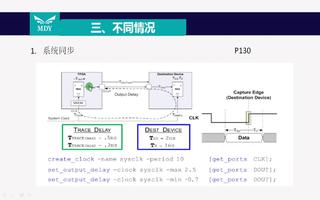

约束流程 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为

2020-11-20 14:44

前面已经提到源同步时钟系统设计中最重要的一点就是保证data和strobe信号之间的偏移(Skew)最小,引起这些误差的最主要的因素就是实际

2014-12-30 14:05

文章目录高温下STM32采用内部晶振作为系统时钟的时钟源导致时序紊乱问题高温导致

2021-12-14 18:58

根据源同步的一些基本问题,在Cadence仿真环境下,对源同步时序进行仿真,仿真结果表明,设计能满足噪声容限和过冲,仿真

2012-05-29 15:26