利用参数可设置模块库(LPM)中的兆功能模块,根据实际系统的需要,对其参数进行必要的调整设置,介绍了一个高速FIFO 存储器的设计方法和步骤,给出了仿真结果,方便实用。

2009-09-02 09:33

FPGA设计的高速FIFO电路技术 本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器

2010-05-27 09:58

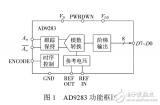

以CPLD为逻辑控制核心实现了ADS8323与高速FIFO的接口电路,该电路具有可靠性高、通用性强、易于移植等特点。在设计过程中,以QuartusII作为开发环境,采用图形输入和Verilog HDL语言输

2010-08-06 14:25

上集成的高速FIFO实现采集数据的高速缓存并通过对高速FIFO的读写操作实现总线同步数据传输,提高数据的传输速率。

2018-07-12 09:06

In First Out)存储器凭借其操作简单、可靠性好等特点,被广泛的应用于数据采集系统中,成为了连接MCU与AD芯片的桥梁。为了使MCU、AD芯片以及高速FIFO存储器能够协调工作,就需要设计好这

2019-05-23 05:01

提出了利用数字信号处理芯片TMS320C6701 和EPM7128 控制两片FIFO 和四片AD9764 的接口电路设计,介绍了AD9764 的基本功能,重点分析了使多片AD9764 和FIFO 在TMS320C6701 系统中稳定工作的关键

2009-08-11 08:48

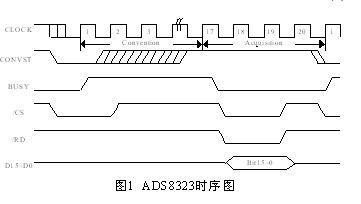

ADS8323需要外接时钟信号,时钟频率范围从25kHZ(1.25kSPS)到10MHZ(500kSPS),其内部的所有动作均与时钟信号同步。工作过程如下:将/CONVST置成低,即可启动转换;在转换过程中,BUSY始终为高;当转换结果被锁存在输出寄存器之后,BUSY变低,此时便可通过将/RD和/CS信号置低读取转换结果。

2019-01-22 16:13

基于FIFO的高速A_D和DSP接口设计

2017-10-19 14:10

高速异步FIFO的设计与实现 引言 现代集成电路芯片中,随着设计规模的不断扩大.一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设

2010-04-12 15:13

本文主要研究了用FPGA 芯片内部的EBRSRAM 来实现异步FIFO 设计方案,重点阐述了异步FIFO 的标志信号——空/满状态的设计思路,并且用VHDL 语言实现,最后进行了仿真验证。

2010-01-13 17:11