高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样

2023-01-05 11:07

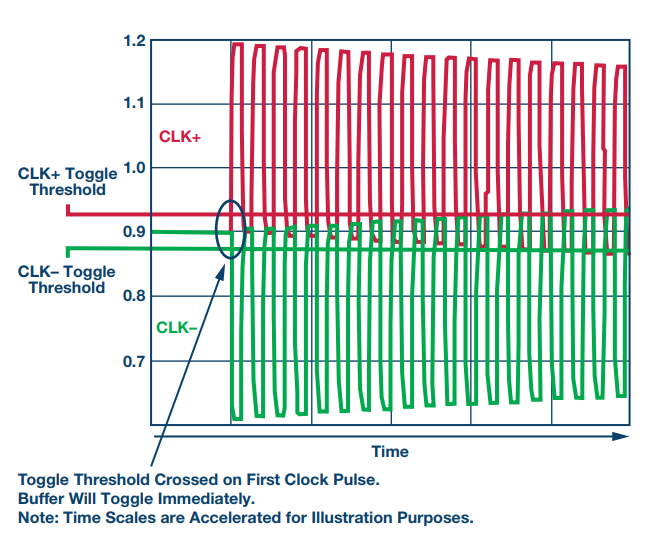

ADC的采样时钟输入端(CLK+和CLK−)。 通常,应使用变压器或电容将该信号交流耦合到CLK+引脚和CLK−引脚内。这两个引脚有内部偏置,无需其它偏置。 高速、高分辨率AD

2017-12-19 04:10

随着使用多模数转换器(ADC)的高速信号采集应用的复杂性提高,每个转换器互补时钟解决方案将决定动态范围和系统的潜在能力。 随着新兴每秒一千兆样本(GSPS) ADC的采

2018-02-11 05:44

如今,在设计人员面临众多电源选择的情况下,为高速ADC设计清洁电源时可能会面临巨大挑战。在利用高效开关电源而非传统LDO的场合,这尤其重要。此外,多数ADC并未给出高频电源抑制规格,这是选择正确电源的一个关键因素。

2015-04-22 09:33

原文标题:编辑推荐:高速ADC测试和评估应用笔记 文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。 审核编辑:彭静

2022-07-04 11:21

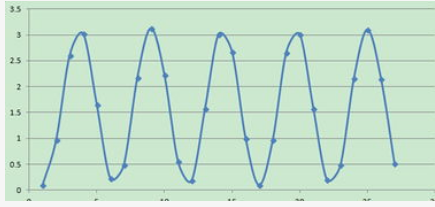

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us; 选择ADC的采样周期为71.5,则ADC时钟频率为:71.4 /(6

2019-10-14 16:22

超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据

2017-11-17 10:40

新型ADC正在朝着低功耗、高速、高分辨率的方向发展,新型流水线结构正是实现高速低功耗ADC的有效方法。而MAX1200则是采用这一新技术的

2012-07-09 15:04

时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速

2019-09-14 11:24

当今许多应用要求高速采样模数转换器(ADC)具有12位或以上的分辨率,以便用户能够进行更精确的系统测量。##电源噪声分析

2014-09-15 18:49