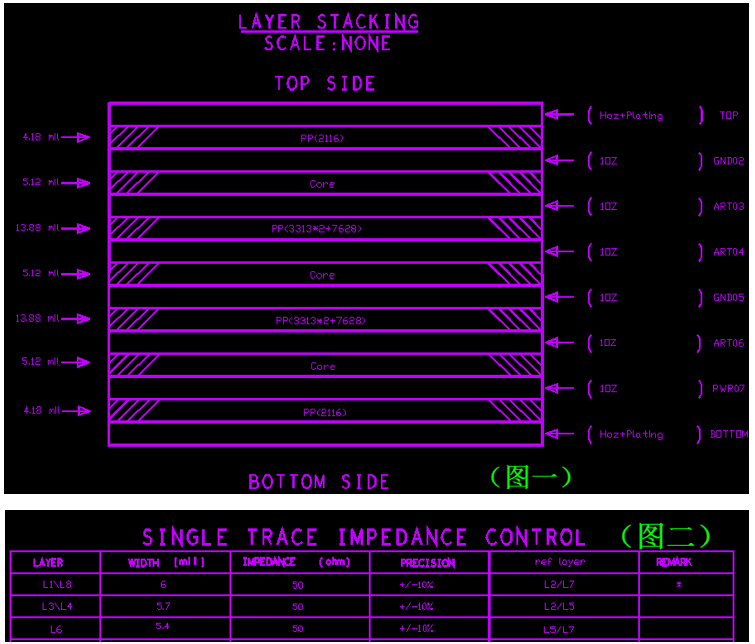

一丶 需要要做阻抗的信号线,应该严格按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分

2020-10-06 20:54

设计的线宽线距应该考虑所选PCB生产工厂的生产工艺能力,如若设计时设置线宽线

2019-10-04 16:35

线宽线距最小控制到 3.5/3.5mil,过孔选择 8mil(0.2mm),这时候有部分PCB生产厂商生产不了,价格会更贵一点。

2019-04-23 17:30

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,

2019-07-01 15:24

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果

2019-03-15 14:05

当涉及到PCB 设计时,PCB 走线电流容量带来的限制是至关重要的。虽然IPC-2221通用设计指南是一个很好的起点,但 PCB

2022-08-22 09:05

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速

2023-05-22 09:15

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,

2018-04-14 11:06

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走

2018-03-08 17:18

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52